-

Hauptmerkmale und Vorteile des Vivado IP Integrator

- Enge Integration in die integrierte Vivado-Designumgebung

- Nahtlose Einbindung der hierarchischen Subsysteme von IP Integrator in das Gesamtdesign

- Schnelle Erfassung und Verpackung von IP Integrator Designs für die Wiederverwendung

- Unterstützung sowohl für grafische als auch für Tcl-basierte Design-Flows

- Schnelle Simulation und Cross-Probing zwischen mehreren Designansichten

- Unterstützung für alle Designdomänen

- Unterstützung für Designs mit und ohne Prozessor

- Integration von Algorithmus-IP (Vitis HLS und Model Composer) und IP auf RTL-Ebene

- Kombination aus DSP, Video, Analog, Embedded, Konnektivität und Logik

- Unterstützung für projektbasierten DFX-Flow

- Fokus auf Designerproduktivität

- DRCs auf komplexen Verbindungen auf Schnittstellenebene während der Designmontage

- Erkennung und Korrektur häufiger Designfehler

- Automatische Propagierung von IP-Parametern an miteinander verbundene IP

- Optimierungen auf Systemebene

- Automatisierte Designerunterstützung

- Verbesserte Unterstützung für die Zusammenarbeit

- Verbesserte Unterstützung für die Zusammenarbeit

- Teambasierte Designs unter Verwendung von Block Design Container ermöglichen Wiederverwendbarkeit und modulare Designs

- Verbesserungen bei der Versionskontrolle durch Trennen von Quelldateien von generierten Dateien

- Block Design Diff Tool zum Vergleich von zwei Blockdesigns

High-Level-Designfunktionen

Hier finden Sie einen kurzen Überblick über die Funktionen der Vivado™ Design Suite zur Beschleunigung von High-Level-Design. Klicken Sie auf die anderen Registerkarten, um vollständige Details zu den Funktionen anzuzeigen.

- Vitis HLS

- IP Integrator

- Abstract Shell

- Vitis Model Composer

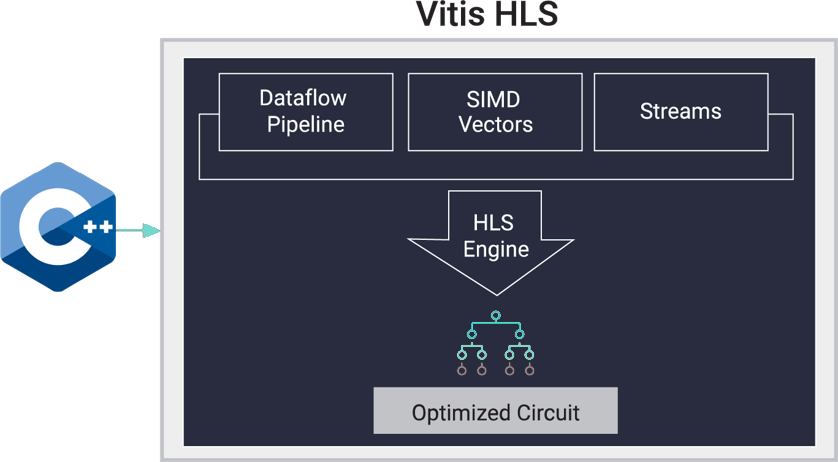

Vitis High-Level Synthesis Tool

Die fortschrittlichen Algorithmen, die heute in KI-, Wireless-, Medizin-, Verteidigungs- und Verbraucheranwendungen verwendet werden, sind ausgefeilter denn je. Das Vitis™ High-Level Synthesis Tool, das als kostenloses Upgrade in allen Vivado™ Editionen enthalten ist, beschleunigt die IP-Erstellung, indem C++-Spezifikationen direkt in programmierbare AMD Chips integriert werden können, ohne dass entsprechende RTL-Designs manuell erstellt werden müssen. Das Vitis HLS Tool unterstützt sowohl die Vitis als auch Vivado-Designumgebungen und ermöglicht Software- und Hardwareentwicklern gleichermaßen die Beschleunigung der Kernel- oder IP-Erstellung durch:

- Abstraktion algorithmischer Beschreibungen, Datentypspezifikationen mit Festkomma- oder Gleitkomma-Ganzzahlen und Schnittstellen (FIFO, Speicher, AXI4)

- Umfangreiche Bibliotheken zur integrierten Unterstützung beliebiger Präzisionsdatentypen, Streams und vektorisierter Datentypen

- Richtlinienbasierte, architekturfähige Synthese mit hoher QoR

- Schnelle Erzielung der QoR, die mit manuell codierter RTL konkurriert

- Beschleunigte Verifizierung unter Verwendung einer C/C++ Testbench-Simulation und automatischer VHDL- oder Verilog-Simulation und Testbench-Erstellung

- Automatische Verwendung von AMD On-Chip-Speichern und DSP-Elementen, auch für Gleitkomma-Arten

Bibliotheken

Die folgenden integrierten Bibliotheken sind im Vitis HLS-Tool enthalten:

| Name | Beschreibung |

|---|---|

Datentypen beliebiger Präzision |

Ganzzahl- und Festkomma(ap_int.h)-Typen |

HLS-Streams |

Modelle für Streaming-Datenstrukturen – entwickelt für beste Leistung und optimale Fläche (hls_stream.h) |

Vektortypen |

Vektorisierte Typen und Operationen (hls_vector.h), einschließlich für Typen beliebiger Präzision |

HLS-Mathematik |

Umfangreiche Unterstützung für die Synthese von mathematischen Standard-C-Bibliotheken (math.h) und C++-Bibliotheken (cmath.h). Unterstützung umfasst Gleitkomma- und Festkommafunktionen: abs, atan, atanf, atan2, atan2, ceil, ceilf, copysign, copysignf, cos, cosf, coshf, expf, fabs, fabsf, floorf, fmax, fmin, logf, fpclassify, isfinite, isinf, isnan, isnormal, log, log10, modf, modff, recip, recipf, round, rsqrt, rsqrtf, 1/sqrt, signbit, sin, sincos, sincosf, sinf, sinhf, sqrt, tan, tanf, trunc |

Das Vitis HLS-Tool unterstützt auch die auf GitHub verfügbaren leistungsoptimierten Vitis-Bibliotheken mit sofortiger Beschleunigung und minimalen Codeänderungen an Ihren vorhandenen Anwendungen. Zu diesen gängigen Vitis Accelerated-Bibliotheken gehören erweiterte Mathematik, Statistik, lineare Algebra und DSP, die Kernfunktionen für eine Vielzahl von Anwendungen bieten. Diese Bibliotheken bieten Beschleunigung für Arbeitslasten wie Vision und Bildverarbeitung mit OpenCV-Funktionen, Quantitative Finance, Datenbank, Datenanalyse, Datenkomprimierung und mehr.

Weitere Informationen finden Sie auf der Vitis HLS-Website.

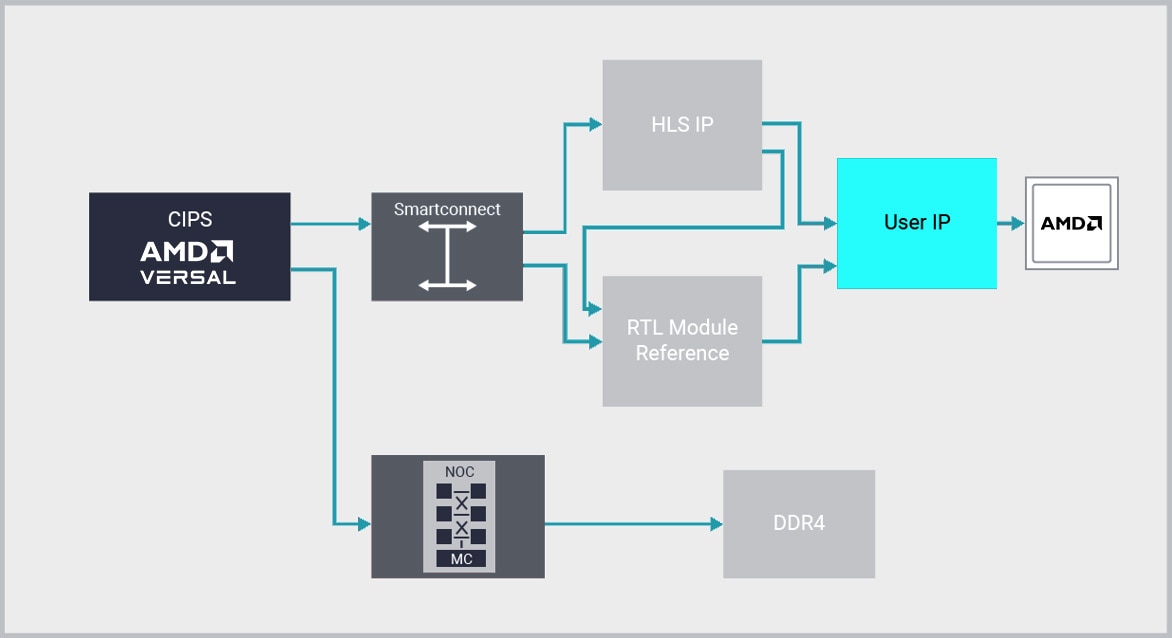

IP Integrator

Die Vivado™ Design Suite durchbricht das Produktivitätsplateau des RTL-Designs, indem es mit seiner IP Integrator-Funktion die branchenweit erste Designumgebung für die IP-Integration per Plug-and-Play bereitstellt.

Vivado IP Integrator bietet einen grafischen und Tcl-basierten Correct-by-Construction-Designentwicklungs-Flow. Er stellt eine Chip- und Plattform-orientierte, interaktive Umgebung bereit, die eine intelligente automatische Verbindung wichtiger IP-Schnittstellen, die Erstellung von IP-Subsystemen per einfachem Mausklick, Echtzeit-DRCs und das Propagieren von Schnittstellenänderungen unterstützt. Dazu kommt eine leistungsstarke Debugging-Funktion.

Designer arbeiten bei der Herstellung von Verbindungen zwischen IP auf der „Schnittstellen“- und nicht auf der „Signal“-Ebene, wodurch die Produktivität erheblich gesteigert wird. Oft werden dabei dem Branchenstandard entsprechende AXI4-Schnittstellen verwendet. IP Integrator unterstützt aber auch Dutzende anderer Schnittstellen.

Auf Schnittstellenebene können Designteams schnell komplexe Systeme zusammenstellen, die IP nutzen, die mit Vitis HLS, Model Composer, AMD SmartCore™ und LogiCORE™ IP, Alliance Member IP sowie Ihrer eigenen IP erstellt wurden. Durch die Nutzung der Kombination aus Vivado IPI und HLS sparen Kunden bis zum 15-Fachen an Entwicklungskosten im Vergleich zu einem RTL-Ansatz.

C-basierte IP-Generierung mit Vitis High-Level Synthesis und Vitis Model Composer

Als führender Anbieter von Tools für Designs auf elektronischer Systemebene für programmierbare Lösungen bietet Vivado Vitis™ High-Level Synthesis für C, C++ und SystemC, und als Add-on kann Vitis Model Composer für DSP erworben werden. Diese Lösungen ermöglichen die direkte Synthese von High-Level-IP-Spezifikationen in VHDL und Verilog und beschleunigen so die IP-Verifizierung um das 100-Fache und die RTL-Erstellung um das 4-Fache. Die hochintegrierten Tools können einzeln oder in Kombination verwendet werden, wobei das Ergebnis eine wiederverwendbare IP für den Einsatz in der Vivado ML Suite ist.

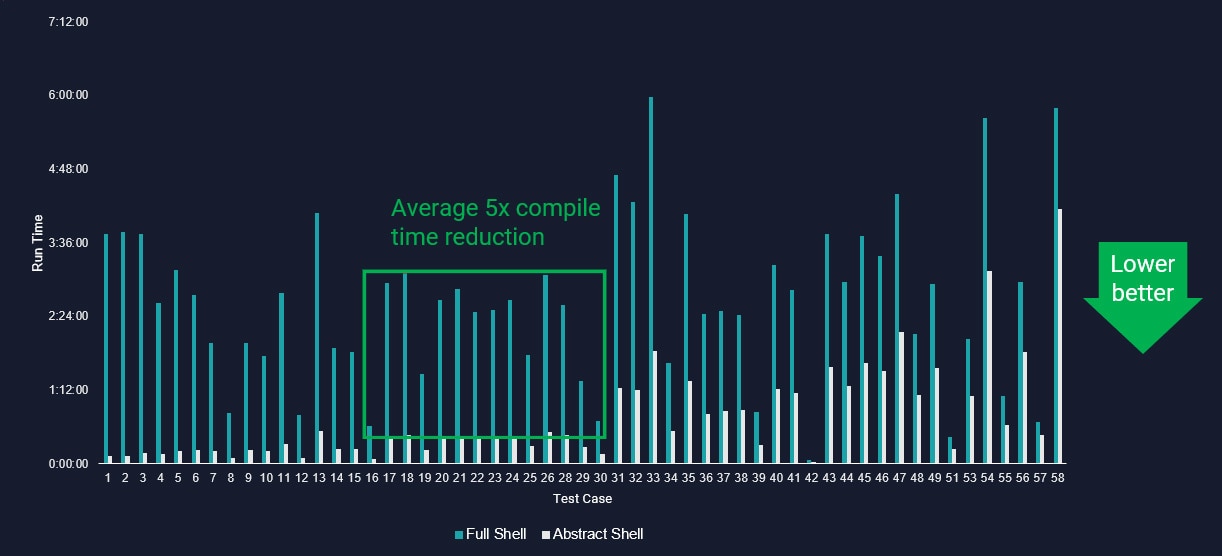

Schnelle Kompilierung unter Verwendung von Abstract Shell

Abstract Shell ist eine neue Technologie, die eine schnelle Kompilierung für komplexe und große Design ermöglicht. Sie ermöglicht es Benutzern, rekonfigurierbare Module innerhalb eines Designs zu definieren, die unabhängig voneinander kompiliert werden. Benutzer können Teile des Designs auswählen, die geändert und neu kompiliert werden sollen, ohne das gesamte Design neu kompilieren zu müssen.

Abstract Shell ermöglicht eine durchschnittliche Reduzierung der Kompilierungszeit um das 5-Fache und um das bis zu 17-Fache im Vergleich zu einer herkömmlichen Kompilierung. Mit diesen Funktionen können Benutzer auch mehrere Module innerhalb des Designs definieren, die parallel kompiliert werden können.

Hauptmerkmale

Abstract Shell ermöglicht Benutzern Folgendes:

- Reduzierung der Laufzeit und Speicherauslastung für jede neu konfigurierbare Modulkompilierung

- Parallele Implementierung aller neu konfigurierbaren Module für mehrere neu konfigurierbare Partitionen

- Ausblenden aller proprietären Informationen aus dem statischen Design

- Vermeidung einer Lizenzprüfung auf IP, die im statischen Design vorhanden sind

- Verteilung neu konfigurierbarer Partitionen auf mehrere Teams für teambasierte Designzusammenarbeit

Erfahrungsberichte

Vitis Model Composer

Der Vitis™ Model Composer ist ein modellbasiertes Design-Tool, das eine schnelle Designprüfung in der MathWorks MATLAB® und Simulink® Umgebung ermöglicht und den Weg zur Produktion auf AMD Chips durch automatische Code-Generierung beschleunigt. Sie können Ihre DSP-Algorithmen entwerfen, sie mithilfe von Performance-optimierten Blöcken auf hoher Ebene ausführen und die funktionale Korrektheit durch Simulationen auf Systemebene validieren. Durch automatische Optimierungen transformiert Vitis Model Composer Ihre Designs für die Implementierung in Produktionsqualität. Das Tool bietet eine Bibliothek mit mehr als 200 HDL-, HLS- und AI-Engine-Blöcken für das Design und die Implementierung von Algorithmen auf AMD Chips. Außerdem können benutzerdefinierte HDL-, HLS- und AI-Engine-Codes als Blöcke in das Tool importiert werden. Vitis Model Composer umfasst alle Funktionen des AMD System Generator für DSP, der seit der Version 2020.2 nicht mehr als eigenständiges Tool ausgeliefert wird.

In Vitis Model Composer ist Folgendes möglich:

- Erstellung eines Designs mit optimierten Blöcken, die auf KI-Engines und programmierbare Logik abzielen

- Visualisieren und Analysieren von Simulationsergebnissen und Vergleich der Ausgabe mit „Golden References“, die mit MALTAB® und Simulink® generiert wurden

- Nahtlose Kosimulation von KI-Engine und programmierbaren Logikblöcken (HLS, HDL)

- Automatische Generierung von Code (KI-Engine-Datenflussdiagramm, RTL, HLS C++) und Prüfung eines Designs auf der Testbench

- Importieren von benutzerdefinierter HLS, KI-Engines und RTL-Codes als Blöcke.

Hinweis:

Vitis Model Composer kann als Add-on-Lizenz für jede Vivado Design Suite Edition erworben werden.

Weitere Informationen zum Herunterladen und Kauf finden Sie auf der Seite Vitis Model Composer.

Hauptmerkmale

-

Beschleunigung von Designiterationen

- Hohe Abstraktionsebene:

Algorithmuszentrische Bausteine mit Schwerpunkt auf Funktionalität bieten eine Benutzerfreundlichkeit, die für Experten unerlässlich ist, um die Untersuchung von Designs zu beschleunigen.

- Unterstützung für Vektoren und Matrizen:

Ermöglicht ein rahmenbasiertes Algorithmusdesign, das Ihnen die Zeit und den Aufwand für ein Zwischenmodell auf niedriger Ebene für die Implementierung spart.

- Anwendungsspezifische Bibliotheken:

Leistungsoptimierte DSP-, Computer Vision-, mathematische und lineare Algebra-Bibliotheken, die als Blöcke für die Simulation und Hochleistungsimplementierung auf AMD Chips verfügbar sind.

- Import von synthetisierbares C/C++ als benutzerdefinierte Blöcke:

Die Möglichkeit, eigene benutzerdefinierte Blöcke für die Simulation und Codegenerierung zu erstellen, bietet größere Flexibilität bei der Entwicklung differenzierter Algorithmen.

- Nahtlose Integration mit Simulink:

Die direkte Verbindung mit Blöcken aus der Simulink Produktfamilie unterstützt die Modellierung und Simulation auf Systemebene und bietet die Möglichkeit, die Funktionen zur Stimulusgenerierung und Datenvisualisierung der grafischen Umgebung von Simulink umfassend zu nutzen.

- Ganzzahl-, Gleitkomma- und Festkommaunterstützung:

Unterstützt die nativen Gleitkomma- und Ganzzahl-Datentypen in Simulink und die Festkomma- und Halbdatentypen, die von Vitis HLS unterstützt werden.

-

Umwandlung von Algorithmen in Architektur

- Automatische Optimierungen:

Analysiert Ihre algorithmischen Spezifikationen in Simulink und führt automatische Optimierungen durch, um eine Mikroarchitektur zu erzielen, die den Durchsatz optimiert, die Auslastung des Block-RAM reduziert und die gleichzeitige Ausführung von Blöcken ermöglicht.

- Beschleunigte IP-Erstellung:

Verwandeln Sie Ihre simulierten Designs in ein RTL-IP-Paket, das Sie in Vivado IP Integrator verwenden können, und nutzen Sie alle Vorteile der Plug-and-Play-Designumgebung für die IP-Integration für komplexe Designs.

- Erweiterung auf Systemgenerator für DSP:

Nutzen Sie die Vorteile der Benutzerfreundlichkeit und Simulationsgeschwindigkeit von Model Composer für Teile Ihres Designs, und exportieren Sie die synthetisierte RTL als neue benutzerdefinierte Blöcke in Ihren vorhandenen Systemgenerator für DSP-Designs.

- Export in Vitis HLS:

Erweiterte Funktion, die eine Verknüpfung zwischen der grafischen Umgebung von Simulink zur Entwicklung, Simulation und Validierung Ihrer Algorithmen und Vitis HLS bietet. Dabei werden automatisch alle erforderlichen Funktionen generiert, mit denen Ihr Algorithmus weiter optimiert wird, einschließlich der in der Simulation protokollierten Testvektoren.

- Benutzeroberfläche zum Zuordnen von RTL-Schnittstellen:

Einfach zu bedienende grafische Benutzeroberfläche zur Zuordnung der Ein- und Ausgänge in Ihrem Design zu unterstützten RTL-Schnittstellen (AXI4-Lite, AXI4-Stream, AXI4-Stream Video, FIFO, Block RAM) und Videoformaten (AXI4-Stream Video) zur Implementierung.

Automatische Erstellung von Testbenches: Automatische Protokollierung von Testvektoren in der Simulation und Generierung einer Testbench zur Überprüfung der funktionalen Äquivalenz zwischen dem ausführbaren Design und dem generierten Code.

- Ganzzahl-, Gleitkomma- und Festkommaunterstützung:

Unterstützt die nativen Gleitkomma- und Ganzzahl-Datentypen in Simulink und die Festkomma- und Halbdatentypen, die von Vitis HLS unterstützt werden.