-

Principaux avantages et fonctionnalités de Vivado IP Integrator

- Intégration étroite dans l'environnement de conception intégré Vivado

- Intégration fluide des sous-systèmes hiérarchiques d'IP Integrator dans la conception globale

- Capture et mise en package rapides des conceptions IP Integrator en vue d'une réutilisation

- Prise en charge des flux de conception graphiques et basés sur Tcl

- Simulation rapide et cross-probing entre plusieurs vues de conception

- Prise en charge de tous les domaines de conception

- Prise en charge des conceptions avec ou sans processeur

- Intégration de l'algorithme (Vitis HLS et Model Composer) et de l'IP de niveau RTL

- Combinaison de signaux DSP, vidéos, analogiques, intégrés, de connectivité et logiques

- Prise en charge du flux DFX basé sur le projet

- Accent mis sur la productivité des concepteurs

- DRC sur des connexions complexes au niveau de l'interface lors de l'assemblage de la conception

- Reconnaissance et correction des erreurs de conception courantes

- Propagation automatique des paramètres IP vers l'IP interconnectée

- Optimisations au niveau du système

- Assistance au concepteur automatisée

- Prise en charge améliorée de la collaboration

- Prise en charge améliorée de la collaboration

- Les conceptions basées sur l'équipe utilisant Block Design Container permettent la réutilisation et la conception modulaire

- Amélioration du contrôle des révisions séparant les fichiers source des fichiers générés

- Outil Block Design Diff pour comparer deux Block Designs

Fonctionnalités de conception de haut niveau

Voici un aperçu des fonctionnalités de Vivado™ Design Suite pour accélérer la conception de haut niveau. Cliquez sur les autres onglets pour obtenir des détails complets sur les fonctionnalités.

- Vitis HLS

- IP Integrator

- Abstract Shell

- Model Composer Vitis

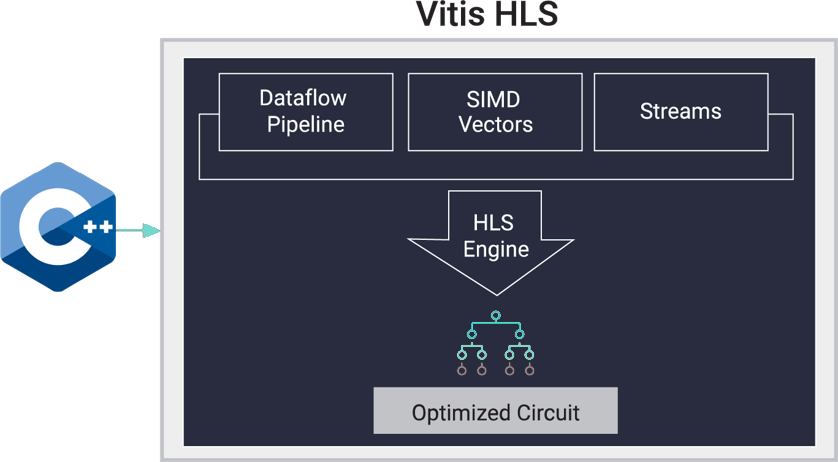

Outil Vitis High-Level Synthesis

Les algorithmes avancés utilisés aujourd'hui dans les applications d'IA, sans fil, médicales, de défense et grand public sont plus sophistiqués que jamais. L'outil Vitis™ High-Level Synthesis, inclus en tant que mise à niveau gratuite dans toutes les éditions de Vivado™, accélère la création d'IP en permettant de cibler directement les spécifications C++ sur les appareils programmables AMD, sans avoir à créer manuellement des conceptions RTL équivalentes. L'outil Vitis HLS prend en charge les environnements de conception Vitis et Vivado, et permet aux concepteurs de software et de hardware d'accélérer la création de kernel ou d'IP grâce à :

- L'abstraction des descriptions algorithmiques, des spécifications de type de données avec des entiers à virgule fixe ou à virgule flottante et des interfaces (FIFO, mémoires, AXI4)

- Des bibliothèques étendues pour inclure un soutien intégré pour les types de données à précision arbitraire, les flux et les types de données vectorisés

- Une synthèse reposant sur les directives et orientée architecture avec une qualité des résultats élevée

- Un délai de qualité des résultats rapide qui rivalise avec le RTL codé à la main

- Une vérification accélérée grâce à la simulation de banc d'essai C/C++, à la simulation VHDL ou Verilog automatique et à la génération de banc d'essai

- L'utilisation automatique des mémoires AMD intégrées et des éléments DSP, y compris pour les types à virgule flottante

Bibliothèques

Les bibliothèques intégrées suivantes sont incluses avec l'outil Vitis HLS :

| Nom | Description |

|---|---|

Types de données de précision arbitraires |

Types entier et à point fixe (ap_int.h) |

Flux HLS |

Modèles de structures de données en streaming : conçus pour obtenir les meilleures performances et la meilleure zone (hls_stream.h) |

Types de vecteurs |

Types et opérations vectorisés (hls_vector.h), y compris pour les types de précision arbitraire |

Mathématiques HLS |

Prise en charge étendue de la synthèse des bibliothèques mathématiques C (math.h) et C++ (cmath.h) standard. La prise en charge inclut les fonctions à virgule flottante et à point fixe : abs, atan, atanf, atan2, atan2, ceil, ceilf, copysign, copysignf, cos, cosf, coshf, expf, fabs, fabsf, floorf, fmax, fmin, logf, fpclassify, isfinite, isinf, isnan, isnormal, log, log10, modf, modff, recip, recipf, round, rsqrt, rsqrtf, 1/sqrt, signbit, sin, sincos, sincosf, sinf, sinhf, sqrt, tan, tanf, trunc. |

L'outil Vitis HLS prend également en charge les bibliothèques optimisées pour les performances Vitis disponibles sur GitHub avec une accélération prête à l'emploi et des modifications de code minimales, voire nulles, pour vos applications existantes. Ces bibliothèques accélérées courantes de Vitis incluent des mathématiques avancées, des statistiques, une algèbre linéaire et un DSP pour offrir des fonctionnalités de base dédiées à une large gamme d'applications. Ces bibliothèques permettent d'accélérer les charges de travail comme la vision et le traitement des images avec les fonctions OpenCV, la finance quantitative, la base de données, l'analyse des données, la compression des données, et bien plus.

Pour plus d'informations, veuillez consulter le site Vitis HLS.

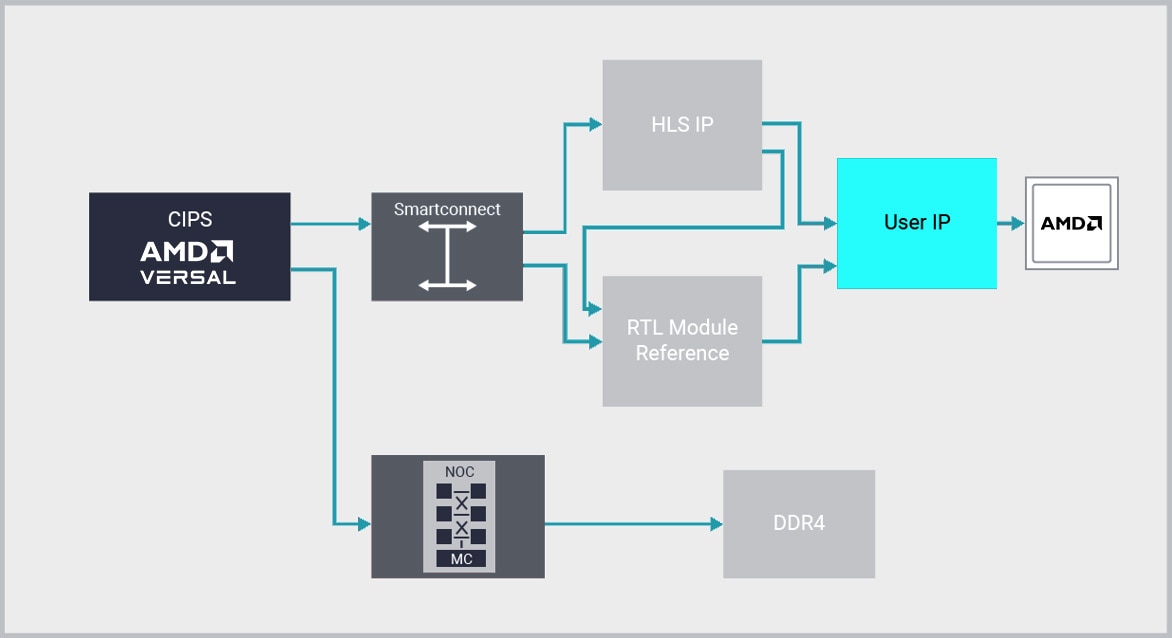

IP Integrator

Vivado™ Design Suite repousse les limites de la productivité pour la conception RTL en fournissant le premier environnement de conception d'intégration IP plug-and-play du secteur, avec sa fonction IP Integrator.

Vivado IP Integrator fournit un flux de développement de conception graphique, basé sur Tcl, correct dès la conception. Il fournit un environnement interactif sensible aux appareils et aux plateformes, qui prend en charge la connexion automatique intelligente des principales interfaces IP, la génération de sous-système IP en un clic, les contrôleurs de domaine en temps réel et la propagation des modifications d'interface, et offre une puissante capacité de débogage.

Les concepteurs travaillent au niveau d'abstraction « interface » et non « signal » lorsqu'ils créent des connexions entre IP, ce qui augmente considérablement la productivité. Le plus souvent, ce sont des interfaces AXI4 standard qui sont utilisées, mais des dizaines d'autres sont également prises en charge par IP Integrator.

En travaillant au niveau de l'interface, les équipes de conception peuvent rapidement assembler des systèmes complexes qui exploitent l'IP créée avec Vitis HLS, Model Composer, AMD SmartCore™ et LogiCORE™ IP, Alliance Member IP ainsi que votre propre IP. Grâce à la combinaison de Vivado IPI et HLS, les clients économisent jusqu'à 15 fois plus sur les coûts de développement, par rapport à une approche RTL.

Génération d'IP basée sur C avec synthèse de haut niveau Vitis et Vitis Model Composer

Principal fournisseur d'outils de conception de systèmes électroniques pour solutions programmables, Vivado fournit une synthèse de haut niveau Vitis™ pour C, C++ et SystemC, et vous pouvez acheter un complément Model Composer Vitis pour DSP. Ces solutions permettent de spécifier des IP de haut niveau à synthétiser directement dans VHDL et Verilog, accélérant la vérification des IP jusqu'à 100 fois et la création de RTL jusqu'à 4 fois. Les outils hautement intégrés peuvent être utilisés individuellement ou en combinaison, le résultat étant réutilisable en tant qu'IP dans la suite ML Vivado.

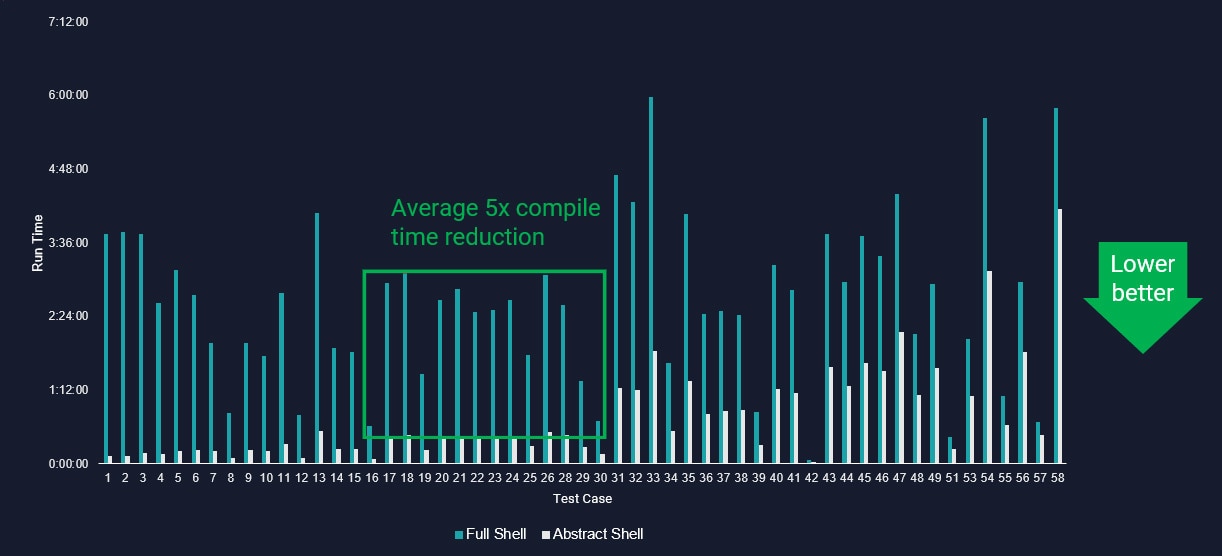

Compilation rapide à l'aide d'Abstract Shell

Abstract Shell est une nouvelle technologie qui permet une compilation rapide pour les conceptions complexes et volumineuses. Elle permet aux utilisateurs de définir des modules reconfigurables au sein d'une conception à compiler indépendamment. Les utilisateurs peuvent sélectionner des parties de la conception à modifier et à recompiler ce qui évite de recompiler l'intégralité de la conception.

Abstract Shell permet de réduire le temps de compilation moyen de 5 fois et jusqu'à 17 fois par rapport à une compilation traditionnelle. Cette fonction permet également aux utilisateurs de définir plusieurs modules au sein de la conception, qui peuvent être compilés en parallèle.

Fonctionnalités clés

Abstract Shell permet aux utilisateurs :

- De réduire le temps d'exécution et l'utilisation de la mémoire pour chaque compilation de module reconfigurable

- De mettre en œuvre tous les modules reconfigurables en parallèle pour plusieurs partitions reconfigurables

- De masquer toutes les informations propriétaires qui existent dans la conception statique

- D'éviter de vérifier les licences pour tout IP qui existe dans la conception statique

- De répartir les partitions reconfigurables entre plusieurs équipes pour une collaboration de conception basée sur les équipes

Témoignages

Model Composer Vitis

Vitis™ Model Composer est un outil de conception basé sur un modèle qui permet une exploration rapide des conceptions dans l'environnement MathWorks MATLAB® et Simulink®, et qui accélère le passage à la production sur les appareils AMD grâce à la génération automatique de code. Vous pouvez concevoir vos algorithmes et les itérer à l'aide de blocs de haut niveau et optimisés pour les performances, et valider l'exactitude fonctionnelle à l'aide de simulations au niveau du système. Vitis Model Composer transforme votre conception en une implémentation de qualité production, grâce à des optimisations automatiques. L'outil offre une bibliothèque de plus de 200 blocs HDL, HLS et AI Engine pour la conception et la mise en œuvre d'algorithmes sur les appareils AMD. Il permet également d'importer du code HDL, HLS et AI Engine personnalisé sous forme de blocs dans l'outil. Vitis Model Composer inclut toutes les fonctionnalités d'AMD System Generator pour DSP, qui n'est plus fourni en tant qu'outil autonome depuis 2020.2.

Dans Vitis Model Composer, vous pouvez :

- Créer une conception à l'aide de blocs optimisés ciblant les moteurs IA et la logique programmable.

- Visualiser et analyser les résultats de simulation et les comparer aux références absolues générées à l'aide de MALTAB® et Simulink®.

- Co-simuler en toute transparence le moteur d'IA et les blocs logiques programmables (HLS, HDL).

- Générer automatiquement du code (graphique de flux de données des moteurs IA, RTL, HLS C++) et un banc d'essai pour une conception.

- Importer des moteurs HLS, AI et RTL personnalisés sous forme de blocs.

Remarque :

Vitis Model Composer peut être acheté sous forme de licence complémentaire pour n'importe quelle édition de Vivado Design Suite.

Pour plus d'informations sur le téléchargement et l'achat, veuillez consulter la page Vitis Model Composer.

Fonctionnalités clés

-

Accélérez les itérations de conception

- Haut niveau d'abstraction :

Les modules centrés sur les algorithmes et axés sur les fonctionnalités offrent une facilité d'utilisation essentielle pour les experts afin d'accélérer l'exploration de la conception.

- Prise en charge des vecteurs et matrices :

Permet de concevoir des algorithmes basés sur des trames, et ainsi d'économiser du temps et des efforts pour passer à un modèle intermédiaire de bas niveau pour la mise en œuvre.

- Bibliothèques spécifiques à l'application :

Bibliothèques DSP, Computer Vision, Math et Linear Algebra optimisées en matière de performances disponibles sous forme de blocs pour la simulation et la mise en œuvre hautes performances sur les appareils AMD.

- Importez le C/C++ synthétisable sous forme de blocs personnalisés :

La possibilité de créer vos propres blocs personnalisés pour la simulation et la génération de code offre une plus grande flexibilité pour concevoir vos algorithmes différenciés

- Intégration fluide avec Simulink :

La connexion directe avec les blocs de la famille de produits Simulink permet la modélisation et la simulation au niveau du système. Elle offre la possibilité de tirer pleinement parti des capacités de génération de stimulus et de visualisation des données de l'environnement graphique de Simulink.

- Prise en charge des nombres entiers, des nombres flottants et des nombres fixes :

Prend en charge les types de données natifs flottants et entiers dans Simulink et les types de données à virgule fixe et à demi-précision pris en charge par Vitis HLS.

-

Transformer l'algorithme en architecture

- Optimisations automatiques :

Analyse vos spécifications algorithmiques dans Simulink et effectue des optimisations automatiques pour s'orienter vers une micro-architecture qui optimise le débit, réduit l'utilisation de la RAM en mode bloc et permet l'exécution simultanée des blocs.

- Accélérer la création d'IP :

Transformez vos conceptions simulées en un package RTL IP que vous pouvez utiliser dans Vivado IP Integrator et tirez parti de tous les avantages de son environnement de conception d'intégration d'IP plug-and-play pour les conceptions complexes.

- Étendre au générateur de système pour DSP :

Tirez parti de la facilité d'utilisation et de la vitesse de simulation de Model Composer pour certaines parties de votre conception, et exportez le RTL synthétisé dans votre System Generator existant pour les conceptions DSP, sous forme de nouveaux blocs personnalisés.

- Exporter vers Vitis HLS :

Fonctionnalité avancée qui fournit un lien entre l'environnement graphique de Simulink pour concevoir, simuler et valider vos algorithmes et Vitis HLS, en générant automatiquement tout ce dont vous aurez besoin pour optimiser davantage votre algorithme, y compris les vecteurs de test enregistrés lors de la simulation.

- Interface utilisateur pour mapper les interfaces RTL :

Interface graphique facile à utiliser pour mapper les entrées et les sorties de votre conception aux interfaces RTL prises en charge (AXI4-Lite, AXI4-Stream, AXI4-Stream Video, FIFO, Block RAM) et aux formats vidéo (AXI4-Stream Video) pour la mise en œuvre.

Génération automatique de banc d'essai : Enregistrement automatique des vecteurs de test à partir de la simulation et de la génération d'un banc d'essai pour vérifier l'équivalence fonctionnelle entre la conception exécutable et le code généré.

- Prise en charge des nombres entiers, des nombres flottants et des nombres fixes :

Prend en charge les types de données natifs flottants et entiers dans Simulink et les types de données à virgule fixe et à demi-précision pris en charge par Vitis HLS.