-

Principaux avantages et fonctionnalités de Vivado IP Integrator

- Intégration étroite dans l'environnement de conception intégré Vivado

- Intégration fluide des sous-systèmes hiérarchiques d'IP Integrator dans la conception globale

- Capture et mise en package rapides des conceptions IP Integrator en vue d'une réutilisation

- Prise en charge des flux de conception graphiques et basés sur Tcl

- Simulation rapide et cross-probing entre plusieurs vues de conception

- Prise en charge de tous les domaines de conception

- Prise en charge des conceptions avec ou sans processeur

- Intégration de l'algorithme (Vitis HLS et Model Composer) et de l'IP de niveau RTL

- Combinaison de signaux DSP, vidéos, analogiques, intégrés, de connectivité et logiques

- Prise en charge du flux DFX basé sur le projet

- Accent mis sur la productivité des concepteurs

- DRC sur des connexions complexes au niveau de l'interface lors de l'assemblage de la conception

- Reconnaissance et correction des erreurs de conception courantes

- Propagation automatique des paramètres IP vers l'IP interconnectée

- Optimisations au niveau du système

- Assistance au concepteur automatisée

- Prise en charge améliorée de la collaboration

- Prise en charge améliorée de la collaboration

- Les conceptions basées sur l'équipe utilisant Block Design Container permettent la réutilisation et la conception modulaire

- Amélioration du contrôle des révisions séparant les fichiers source des fichiers générés

- Outil Block Design Diff pour comparer deux Block Designs

Présentation

AMD Vivado™ prend en charge la conception en HDL traditionnel comme VHDL et Verilog. Elle prend également en charge un outil basé sur une GUI (interface graphique utilisateur) appelé IP Integrator (IPI), qui permet de créer un environnement de conception d'intégrations IP plug-and-play.

Vivado offre la meilleure synthèse et la meilleure implémentation de sa catégorie pour les FPGA et les SoC complexes d'aujourd'hui, avec des capacités intégrées de fermeture temporelle et de méthodologie.

Le rapport de méthodologie UltraFast™ (report_methodology) disponible dans le flux par défaut de Vivado aide les utilisateurs à définir des contraintes pour leur conception, à analyser les résultats et à faire la fermeture temporelle.

Fonctionnalités

Voici un aperçu des fonctionnalités de Vivado™ Design Suite pour l'entrée et l'implémentation des conceptions. Cliquez sur les autres onglets pour obtenir tous les détails sur les fonctionnalités.

- IP Integrator

- Synthèse logique

- Méthodologie de conception

- Implémentation

IP Integrator

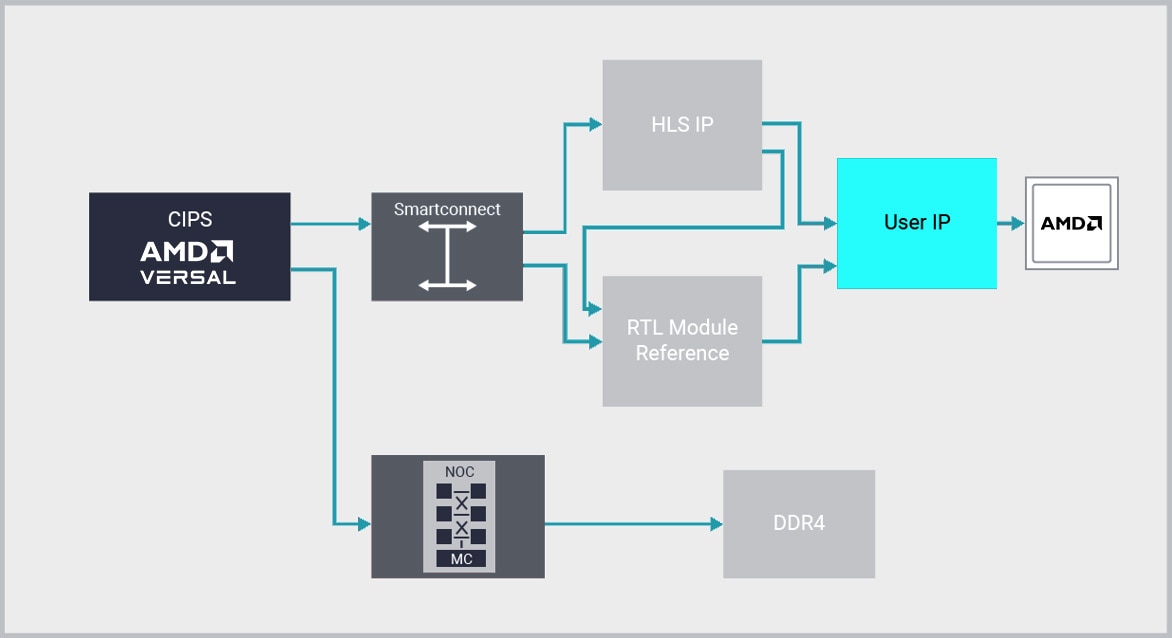

AMD Vivado™ repousse les limites de la productivité pour la conception RTL en fournissant le premier environnement de conception d'intégration IP plug-and-play du secteur, avec sa fonction IP Integrator.

Vivado IP Integrator fournit un flux de développement de conception graphique, basé sur Tcl, correct dès la conception. Il fournit un environnement interactif sensible aux appareils et aux plateformes, qui prend en charge la connexion automatique intelligente des principales interfaces IP, la génération de sous-système IP en un clic, les contrôleurs de domaine en temps réel et la propagation des modifications d'interface, et offre une puissante capacité de débogage.

Les concepteurs travaillent au niveau d'abstraction « interface » et non « signal » lorsqu'ils créent des connexions entre IP, ce qui augmente considérablement la productivité. Le plus souvent, ce sont des interfaces AXI4 standard qui sont utilisées, mais des dizaines d'autres sont également prises en charge par IP Integrator.

En travaillant au niveau de l'interface, les équipes de conception peuvent rapidement assembler des systèmes complexes qui exploitent l'IP créée avec Vitis HLS, Model Composer, AMD SmartCore™ et LogiCORE™ IP, Alliance Member IP ainsi que votre propre IP. Grâce à la combinaison de Vivado IPI et HLS, les clients économisent jusqu'à 15 fois plus sur les coûts de développement, par rapport à une approche RTL.

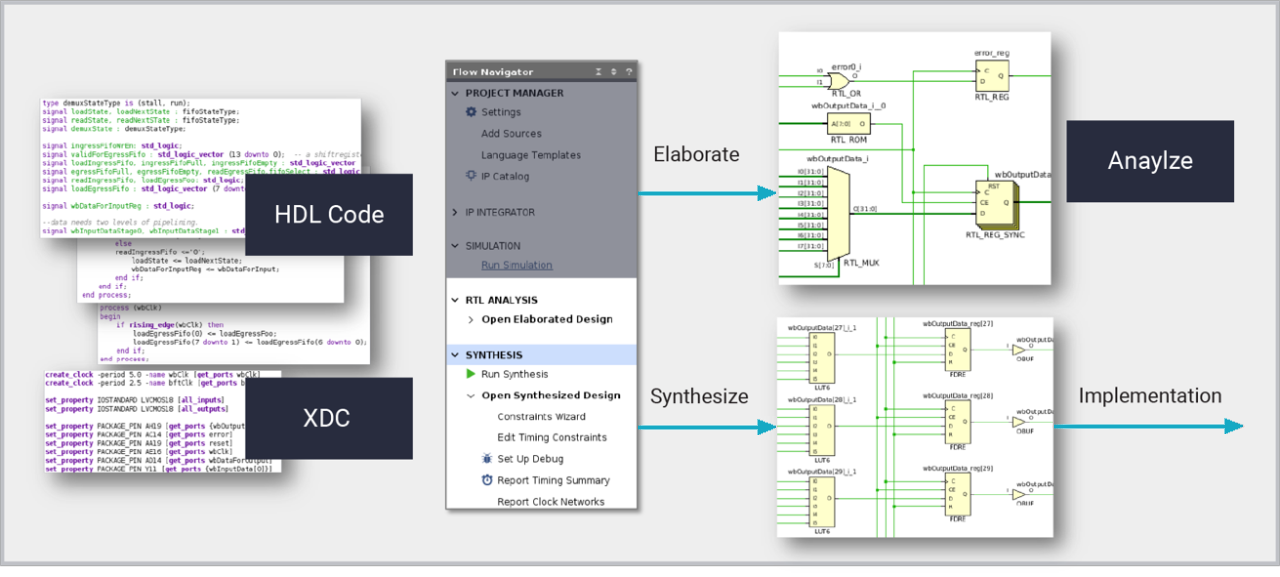

Synthèse logique

Vivado Logic Synthesis est un outil de création de conceptions permettant aux concepteurs hardware de produire des plateformes, des IP et des conceptions personnalisées de qualité optimale, pour tous les appareils AMD les plus récents. La synthèse logique transforme les descriptions RTL (Register Transfer Level) écrites dans SystemVerilog, VHDL et Verilog en une description structurelle synthétisée des cellules de la bibliothèque pour l'implémentation en aval. En tenant compte de la technologie cible, la synthèse peut déduire des fonctions des descriptions RTL, qui sont directement mappées sur les structures en silicium dédiées, notamment les LUTRAM, les blocs-RAM, les registres de shift, les soustracteurs-additionneurs et les blocs DSP. Les résultats de synthèse sont générés à l'aide d'attributs, d'options d'outils et de contraintes de conception Xilinx (XDC) pour atteindre les objectifs de conception. La synthèse logique fonctionne dans les projets Vivado et les scripts Tcl et fournit une base solide pour d'autres méthodes de conception de haut niveau qui génèrent des descriptions RTL, y compris la synthèse de haut niveau et IP Integrator.

La synthèse logique utilise désormais l'apprentissage automatique pour accélérer la compilation. Les modèles de ML améliorent l'efficacité globale en prévoyant les optimisations de synthèse nécessaires pour les différentes parties de la conception.

-

Fonctionnalités clés

- Prise en charge des langages

La synthèse logique prend en charge les dernières constructions synthétisées conformes aux normes de l'industrie :

- Langages de description du matériel (HDL) SystemVerilog, Verilog, VHDL et VHDL-2008

- Possibilité d'utiliser différents types de HDL dans la même conception et de transmettre des paramètres et des génériques à chaque type

- Modèles de langage pour garantir un mappage fiable des fonctions complexes supposées vers les ressources appropriées de l'appareil

Les descriptions des HDL peuvent être examinées visuellement à l'aide d'un schéma de conception élaboré qui effectue un cross probe vers le code source HDL associé.- Contrôle de l'optimisation

La synthèse logique permet de contrôler tous les aspects de l'inférence et de l'optimisation. Il est possible de les affecter :

- À l'utilisation globale des options d'outil et de commande

- Aux modules ou instances spécifiques de hiérarchie logique à l'aide de la contrainte XDC BLOCK_SYNTH

- Aux cellules et réseaux utilisant des attributs HDL

Les différents types de contrôle permettent de :- Conserver, aplatir et reconstruire la hiérarchie

- Déduire ou non des structures spécifiques à la technologie

- Sélectionner le type de ressources mémoire dédiées utilisées pour le mappage des matrices de mémoire

- Attribuer le type de codage pour les machines à état fini (FSMS)

- Donner la priorité aux performances, à l'utilisation ou à la consommation énergétique

- Appliquer des optimisations avancées telles que la resynchronisation logique

- Convertir des horloges synchronisées en signaux d'activation de registre

- Options de compilation

La synthèse logique Vivado prend en charge tous les niveaux de personnalisation, du fonctionnement contrôlé par bouton à l'exploration de différentes stratégies de compilation.

Synthèse logique :

- Fonctionne avec les projets Vivado et les flux hors projet

- Peut être exécutée de manière interactive ou en mode batch à l'aide de scripts Tcl

- Exécute plusieurs processus pour réduire les temps de compilation

- Fournit des stratégies de compilation pour explorer des solutions pour différents objectifs de conception

- Prend en charge un mode de compilation incrémentielle qui réutilise les données des exécutions précédentes pour accélérer les itérations de compilation

Méthodologie de conception

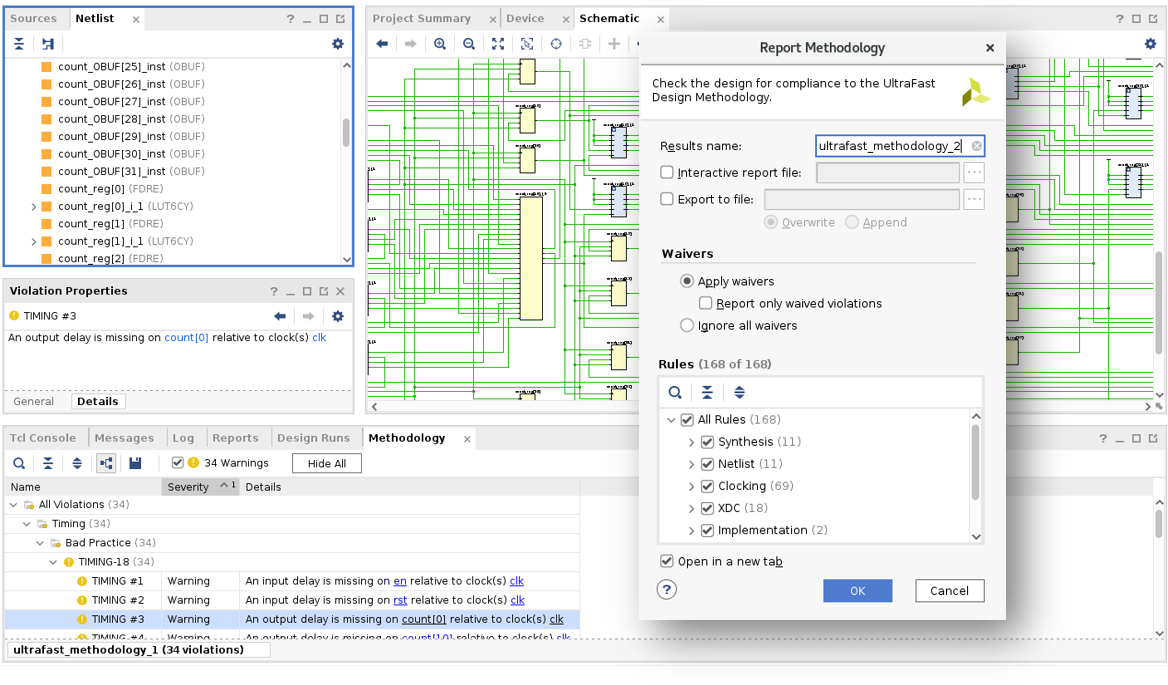

Lorsqu'elle est utilisée avec Vivado, la méthodologie UltraFast permet de définir les contraintes appropriées, de piloter correctement les outils et d'analyser les résultats, et d'améliorer la productivité globale. La méthodologie de conception UltraFast™ est un ensemble de bonnes pratiques de conception hardware, fruit des nombreuses années d'expérience et des succès des experts Vivado en matière de conception pour les clients, qui repoussent les limites des outils et de la technologie.

Fonctionnalités clés

Méthodologie intégrée

Afin de faciliter la conformité aux directives de la méthodologie UltraFast, les rapports de méthodologie UltraFast sont intégrés à Vivado et générés par défaut pour les projets Vivado, ce qui permet de profiter des avantages d'UltraFast sans avoir à lire la documentation. La fonctionnalité Méthodologie de rapport génère une liste des violations de méthodologie détectées dans la conception, réparties par catégorie et niveau de gravité, pour une révision interactive. L'examen et la résolution des violations de méthodologie garantissent que les conceptions sont sur le point de départ optimal pour l'implémentation, pour obtenir les plus grandes chances de réussite, dans les plus brefs délais. Les violations jugées acceptables peuvent être annulées afin de ne pas réapparaître dans les rapports.

Fournir des contraintes complètes et correctes est un élément important de la méthodologie UltraFast. L'assistant de contraintes temporelles (TCW) analyse les contraintes temporelles et fournit des conseils étape par étape sur les contraintes manquantes et la résolution des contraintes non valides. L'exhaustivité des contraintes réduit les risques de bugs du hardware résultant de chemins de synchronisation non contraints, tandis que les contraintes non valides peuvent rediriger les efforts de compilation vers une criticité erronée des délais.

La qualité des contraintes d'alimentation est essentielle pour analyser précisément la consommation énergétique. L'outil Power Constraints Advisor analyse l'activité de commutation de la conception, identifie les zones qui semblent incorrectes et génère des contraintes d'alimentation XDC clé en main pour une analyse appropriée. Les rapports Vivado sur la consommation énergétique incluent également un niveau de confiance indiquant une spécification de contrainte faible, moyenne ou élevée, et fournissent un retour sur l'exhaustivité des contraintes d'alimentation. Un niveau de confiance élevé garantit une analyse de la consommation énergétique extrêmement précise, correspondant étroitement aux mesures du hardware.

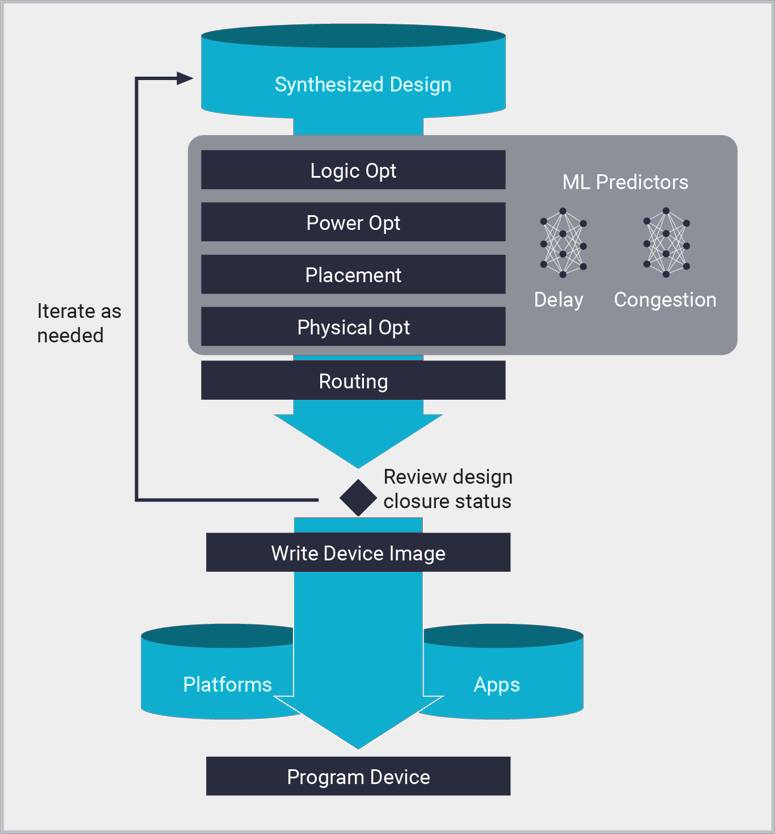

Implémentation

Vivado est l'outil de placement et de routage pour les appareils AMD. Il génère des bitstreams et des images d'appareils à partir d'une description structurelle synthétisée. L'implémentation de Vivado permet de créer des plateformes et des conceptions personnalisées de toutes tailles, des plus petits MPSoC aux plus grands appareils SSIT monolithiques contenant des millions de cellules logiques. L'implémentation de Vivado repose sur des algorithmes de partitionnement, de placement et de routage de pointe, guidés par des prédicteurs basés sur l'apprentissage automatique. L'application de modèles de ML permet d'améliorer la qualité des résultats dans un délai plus court, avec une prévision précise des retards et des encombrements. L'implémentation est pilotée par Xilinx Design Constraints (XDC) pour atteindre les objectifs de conception en matière de performances, d'utilisation, de consommation d'énergie et de synthèse dans les projets Vivado et les scripts Tcl.

L'implémentation prend en charge tous les modes de fonctionnement, du mode bouton pour une plus grande facilité d'utilisation, aux scripts Tcl personnalisés sophistiqués, pour gérer des conceptions avec les exigences de performances les plus élevées. Une analyse détaillée des délais, de l'utilisation, de la consommation d'énergie et d'autres mesures de qualité de la conception peut être effectuée à n'importe quelle étape de la compilation : pré-placement, post-placement et post-routage. La base de données de conception peut également être enregistrée et restaurée à n'importe quelle étape de la compilation à l'aide de fichiers de point de contrôle de conception (DCP) et la conception peut être visualisée et contrainte en conséquence.

Fonctionnalités clés

-

Processus d'implémentation de Vivado

- Optimisation logique :

Après la synthèse, la description structurelle logique est optimisée globalement afin de réduire l'utilisation et les niveaux logiques.

- Optimisation de la consommation d'énergie :

La consommation d'énergie de la conception est réduite à l'aide de techniques de contrôle d'activité, sans intervention requise, sans modification des fonctionnalités et avec un impact minimal sur les délais.

- Placement :

Les cellules logiques de la description structurelle sont placées dans les ressources des appareils physiques, en fonction des contraintes XDC qui incluent les exigences de synchronisation, de plan et de placement manuel. Le placement commence avec les ressources globales, y compris les ressources d'E/S et d'horloge, et les clusters logiques conformément à la hiérarchie de la conception. La phase de placement global est suivie des phases détaillées de placement et d'optimisation post-placement. Le placement est guidé par des modèles de ML qui prédisent les ralentissements et les congestions de routage, ce qui permet d'obtenir une plus grande précision et une compilation plus rapide qu'avec les méthodes statistiques traditionnelles.

- Routage :

Les connexions entre les différents composants de la description structurelle sont affectées aux ressources d'interconnexion des appareils physiques. Comme pour le placement, le routage commence avec les ressources globales comme les E/S et l'horloge, puis hiérarchise les affectations de ressources en fonction des contraintes de synchronisation XDC. Les phases finales de routage optimisent encore davantage les routes pour répondre aux exigences de configuration des approbations. En utilisant le ML pour prédire les congestions de trafic pendant la phase de placement, il est possible de réduire la congestion.

- Optimisation physique :

L'optimisation physique est un processus basé sur la synchronisation qui se déroule tout au long des phases de placement et de routage. Contrairement à l'optimisation logique, l'optimisation physique utilise les données de synchronisation disponibles les plus précises, en fonction du placement et du routage. L'impact de la synchronisation est évalué de façon que seule l'optimisation appliquée améliore la synchronisation. Les techniques d'optimisation comprennent la réplication, la resynchronisation et le re-placement des registres, ainsi que d'autres optimisations spécifiques à l'architecture cible. L'optimisation physique peut également être effectuée séparément après le placement et le routage, afin d'améliorer encore davantage les résultats.

- Le centre des capacités d'analyse :

Une conception peut être analysée à n'importe quelle étape de la compilation durant l'implémentation. Il s'agit d'un système de gestion des contraintes XDC complet permettant de modifier et de vérifier les contraintes physiques, de synchronisation et de consommation énergétique.

- Rapport de synthèse de synchronisation

Il s'agit d'un puissant analyseur de synchronisation statique, qui prend en charge les contraintes XDC pour guider l'implémentation afin d'atteindre les objectifs de synchronisation spécifiés. Il génère des rapports de synchronisation des chemins de synchronisation critiques, des interactions d'horloge et des croisements de domaines d'horloge (VDC).

- Rapport sur la consommation énergétique :

Propagation sans vecteur, prenant en charge l'activité de commutation XDC pour l'analyse de la consommation d'énergie. Il génère des rapports pour identifier les zones où la consommation d'énergie est plus élevée.

- Vue de l'appareil :

Représentation graphique du placement et du routage de la conception, ainsi que des schémas de la description structurelle logique. Permet d'effectuer un cross-probing entre les vues de conception physique, logique et de code source pour identifier rapidement les sources des chemins de synchronisation critiques.

-

Options de compilation

- Implémentation de Vivado

Prend en charge tous les niveaux de personnalisation, du fonctionnement à l'aide d'un bouton à l'exploration de différentes stratégies de compilation et de flux itératifs pour les conceptions avec des exigences élevées.

- Implémentation

- Fonctionne avec les projets Vivado et les flux hors projet

- Peut être exécutée de manière interactive ou en mode batch à l'aide de scripts Tcl

- Exécute plusieurs threads pour réduire les temps de compilation

- Fournit des stratégies de compilation pour explorer des solutions pour différents objectifs de conception

- Prend en charge un mode de compilation incrémentielle qui réutilise les données des exécutions précédentes, ce qui permet de donner la priorité soit à l'accélération de la compilation, soit à la fermeture temporelle