25G IEEE 802.3by Reed-Solomon Forward Error Correction

作者: AMD

AMD LogiCORE™ 25G IEEE 802.3by RS-FEC IP core 可實現 Reed-Solomon 前向錯誤修正 (Reed-Solomon Forward Error Correction, RS-FEC) 子層。

- 零件編號:

- EF-DI-25G-RS-FEC-SITE

- EF-DI-25G-RS-FEC-PROJ

- 設計工具支援: Vivado Software

- 授權: Core License Agreement

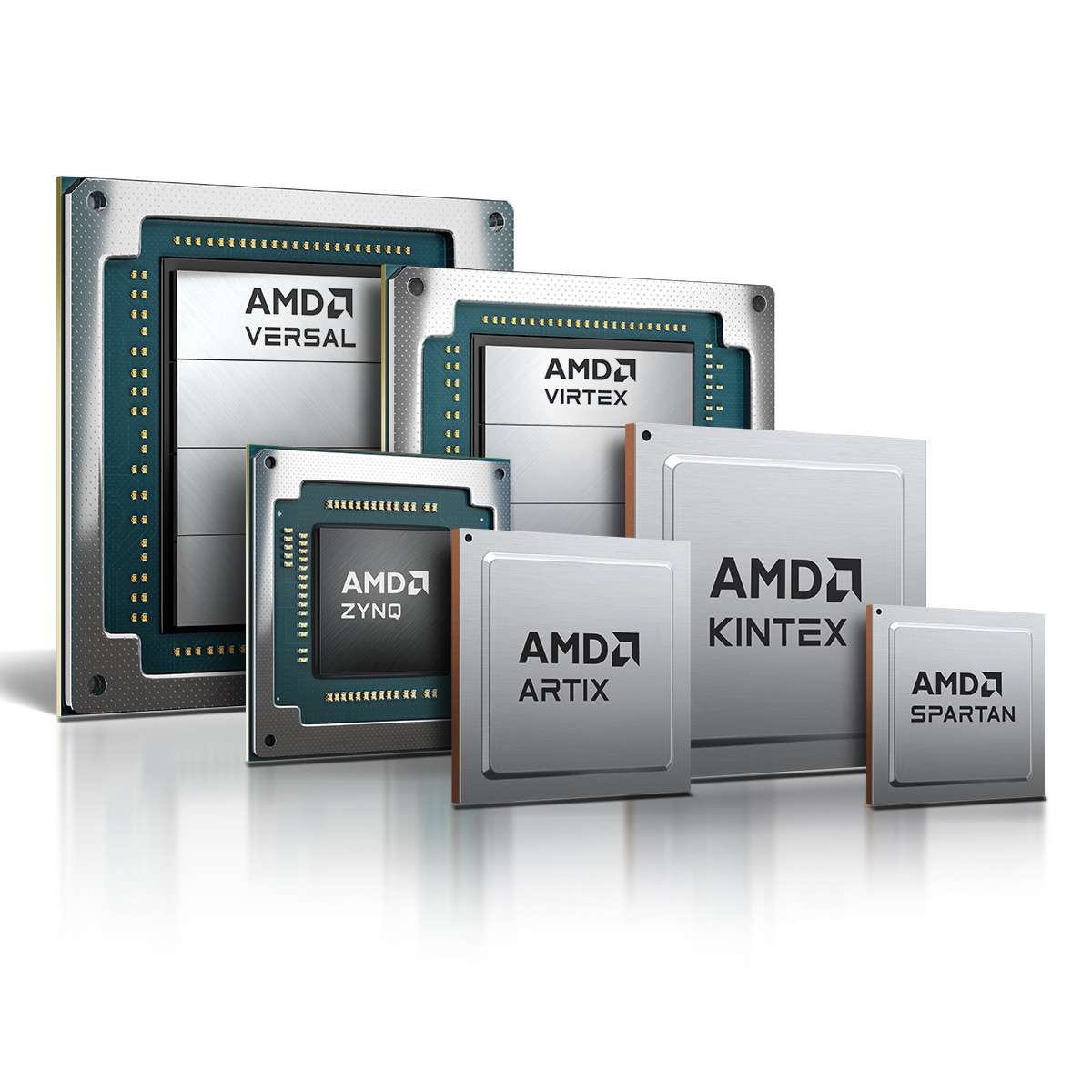

- 器件支援: Kintex UltraScale+, Virtex UltraScale, Virtex UltraScale+, Versal AI Core, Versal Prime, Zynq UltraScale+ RFSoC, Zynq UltraScale+ MPSoC