- 概述

- 現在開始

概述

AMD Vitis™ 求解器程式庫提供一系列效能最佳化的矩陣分解、線性/特徵值求解器和其他函數,這些函數可用於設計雷達、LiDAR、電腦視覺、計算金融和其他應用的加速演算法。

Vitis 求解器程式庫內核可當作獨立加速器,並在嵌入式/主機程式碼中呼叫,也可以結合其他 Vitis 程式庫內核和基元使用,以加速端對端處理管道。

目前可用的部分關鍵加速函數,包括奇異值分解 (SVD)、QR 與 LU(上下三角矩陣)分解、矩陣求逆、三角求解器與特徵值分解等。

功能

針對稠密矩陣,目前 Vitis 求解器程式庫收錄了以下運算法:

矩陣分解

- Cholesky 分解,適用於對稱正定矩陣

- 不軸轉 (pivoting) 及部分軸轉的 LU 分解

- 一般矩陣的 QR 分解

- 對稱和非對稱矩陣 SVD(奇異值分解)(Jacobi 法)

線性求解器

- 三對角線性求解器(平行循環約化法)

- 三角矩陣線性求解器

- 對稱及非對稱矩陣的線性求解器

- 對稱及非對稱矩陣的矩陣求逆

特徵值求解器

- 對稱矩陣的 Jacobi 特徵值求解器

可程式化邏輯 (PL) 與 AI 引擎 (AIE) 陣列函數清單

Vitis 求解器程式庫的目標對象是 Vitis 內核開發人員,意在協助他們加速應用開發。此程式庫提供 L1 和 L2 兩層 API。L1 和 L2 的函數列於下表。

Vitis 求解器程式庫 2022.2 版新增兩個 AI 引擎函數:QR 分解和 Cholesky 分解。

| 求解器程式庫函數 | |

|---|---|

| L1 | QR(正交旋轉)分解 |

| QR_Inverse | |

| SVD(奇異值分解) | |

| Cholesky_Inverse | |

| Cholesky 分解 | |

| QR 分解(適用於 AIE) | |

| Cholesky 分解(適用於 AIE) | |

| L2 | 矩陣分解 |

| 特徵值求解器 | |

| 線性求解器 | |

L1 和 L2 API 特點說明如下

| L1 API | 用於矩陣分解的函數。設計成具備記憶體介面的高階合成 (High-level synthesis, HLS) 元件(指向 BRAM 或 URAM)。這類 API 支援多種資料類型,包括浮點、雙精度或複數。由於 L1 API 要求所有輸入資料都必須在記憶體中就緒,所以輸入矩陣的總大小有其上限。 |

|---|---|

| L2 API | 在 FPGA 器件執行的內核。這類 API 支援雙精度浮點類型。它們讀取 DDR/HBM 以取得輸入資料,然後寫入 DDR/HBM 以輸出結果。可從主控端呼叫。 |

結構

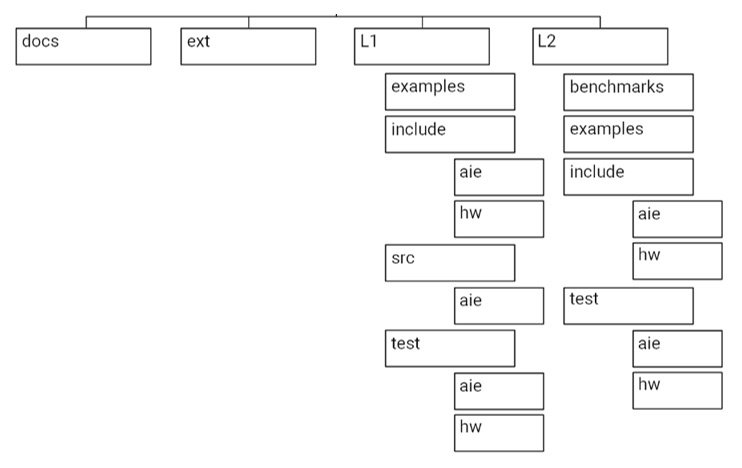

Vitis 求解器程式庫按照不同的應用開發階段,分為 L1 和 L2 資料夾。

L1:L1 中的 Makefile 與來源,可用來推進以 HLS 為基礎的流程,達到快速檢查的效果。

L2:L2 中的 Makefile 與來源,有助於運用各種來源類型的內核(HDL、HLS 或 XO 檔案)建置 XCLBIN 檔案,其中的主機程式碼,是以針對器件的 OpenCL™/Vitis 執行階段程式庫框架所編寫。