- Übersicht

- Erste Schritte

Übersicht

Die AMD Vitis™ Solver-Bibliothek bietet eine Sammlung Performance-optimierter Matrixzerlegungs- und linearer/Eigenwert-Solver sowie weitere Funktionen, die für die Entwicklung beschleunigter Algorithmen für RADAR, LiDAR, Computer-Vision, Computational Finance und andere Anwendungen verwendet werden können.

Die Kernel der Vitis Solver-Bibliothek können Sie als eigenständige Beschleuniger verwenden. Sie können sie in Ihrem integrierten/Host-CPU-Code aufrufen oder mit anderen Kernels und Primitiven der Vitis Bibliothek kombinieren, um Ihre End-to-End-Verarbeitungspipeline zu beschleunigen.

Zu den derzeit verfügbaren Beschleunigungsfunktionen gehören Singulärwertzerlegung (Singular Value Decomposition, SVD), QR und LU (Lower-Upper)-Zerlegung, Kehrmatrix, Dreiecksmatrix-Solver, Eigenwertzerlegung und andere.

Funktionen

Derzeit umfasst die Vitis Solver-Bibliothek die folgenden Vorgänge für dichte Matrizen:

Matrixzerlegung

- Cholesky-Zerlegung für symmetrisch positiv definite Matrizen

- LU-Zerlegung ohne und mit partieller Pivotisierung

- QR-Zerlegung für allgemeine Matrizen

- SVD (Singulärwertzerlegung) für symmetrische und nicht symmetrische Matrizen (Jacobi-Methode)

Linearer Solver

- Solver für lineare Tridiagonalmatrizen (parallele zyklische Reduktionsmethode)

- Linearer Solver für Dreiecksmatrizen

- Linearer Solver für symmetrische und nicht symmetrische Matrizen

- Kehrmatrix für symmetrische und nicht symmetrische Matrizen

Eigenwert-Solver

- Jacobi-Eigenwert-Solver für symmetrische Matrizen

Funktionsliste der programmierbaren Logik (PL)- und AI Engine (AIE)-Arrays

Die Vitis Solver-Bibliothek richtet sich an Vitis Kernel-Entwickler, die ihre Anwendungsentwicklung beschleunigen möchten. Die Bibliothek bietet zwei API-Ebenen, nämlich L1 und L2. Die L1- und L2-Funktionen sind in der folgenden Tabelle aufgeführt.

In der Version 2022.2 der Vitis Solver-Bibliothek wurden zwei neue KI-Engine-Funktionen hinzugefügt: QR-Zerlegung und Cholesky-Zerlegung.

| Funktionen der Solver-Bibliothek | |

|---|---|

| L1 | QR-Zerlegung (Quadrature Rotation) |

| QR_Inverse | |

| SVD (Singularwertzerlegung) | |

| Cholesky_Inverse | |

| Cholesky-Zerlegung | |

| QR-Zerlegung für AIE | |

| Cholesky-Zerlegung für AIE | |

| L2 | Matrixzerlegung |

| Eigenwert-Solver | |

| Linearer Solver | |

Die Funktionen der L1- und L2-APIs werden nachfolgend beschrieben

| L1-APIs | Funktionen für die Matrixzerlegung. Entwickelt als HLS-Komponenten mit Speicherschnittstellen (die auf BRAM oder URAM verweisen). Diese APIs unterstützen eine Vielzahl von Datentypen, einschließlich Float, Double oder Complex. Da für L1-APIs alle Eingabedaten im Speicher abrufbereit sein müssen, haben sie einen oberen Grenzwert für die Gesamtgröße der Eingabematrix. |

|---|---|

| L2-APIs | Kernel, die auf den FPGA-Chips ausgeführt werden. Diese APIs unterstützen Gleitkommatypen mit doppelter Präzision. Das Lesen von Eingaben wie auch das Schreiben von Ergebnissen erfolgt über DDR/HBM. Sie können von der Host-Seite aus aufgerufen werden. |

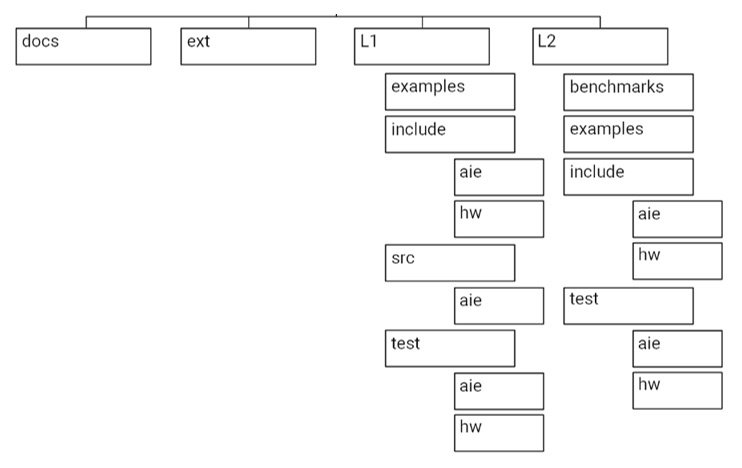

Organisation

Die Vitis Solver-Bibliothek ist in L1- und L2-Ordner unterteilt, die jeweils eine andere Phase der Anwendungsentwicklung betreffen.

L1: Makefiles und Quellen in L1 erleichtern einen HLS-basierten Flow für schnelle Prüfungen.

L2: Makefiles und Quellen in L2 erleichtern das Erstellen der XCLBIN-Datei aus verschiedenen Quellen (HDL-, HLS- oder XO-Dateien) von Kernels. Der Hostcode wurde dabei in einem OpenCL™-/Vitis Laufzeitbibliothek-Framework geschrieben, das auf einen Chip abzielt.