USXGMII Subsystem

作者: AMD

Universal Serial 10GE Media Independent Interface (USXGMII) IP 核心實現一個乙太網路媒體存取控制器 (Media Access Controller, MAC),內含機制可在電機電子工程師學會 (Institute of Electrical and Electronics Engineers, IEEE) 802.3 條款 49 BASE-R 實體編碼子層 (Physical Coding Sublayer, PCS)/實體層 (Physical Layer, PHY) 承載單一個 10M、100M、1G、2.5G、5G 或 10GE 的埠。

- 零件編號:

- EF-DI-USXGMII-MAC-SITE

- 設計工具支援: Vivado Software

- 授權: Core License Agreement

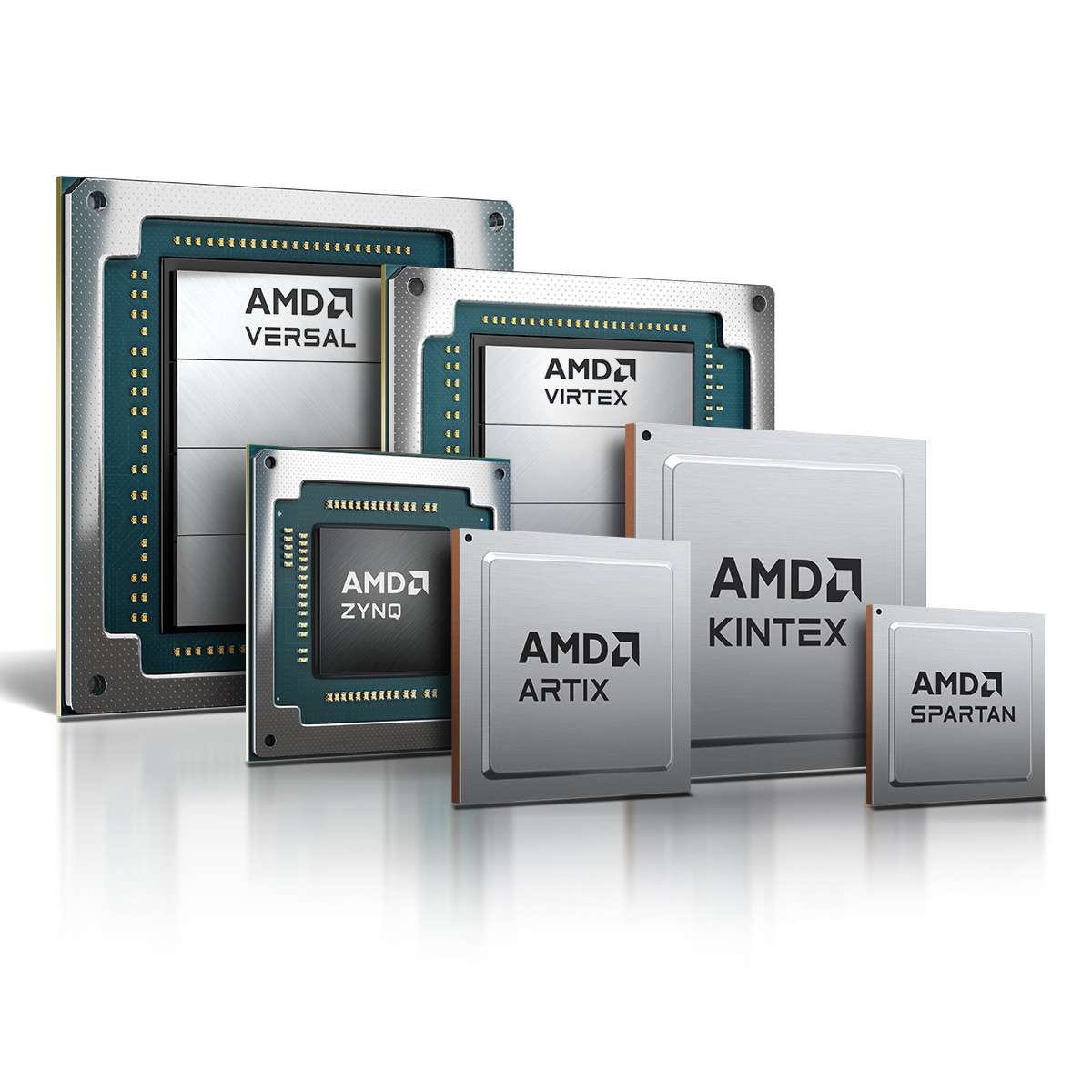

- 器件支援: Kintex UltraScale, Kintex UltraScale+, Artix UltraScale+, Virtex UltraScale, Virtex UltraScale+, Virtex 7, Zynq UltraScale+ MPSoC, Versal AI Core, Versal Prime