概述

企業原型設計是一種結合模擬與傳統原型設計的新興市場,其所提供的解決方案除錯能力更強、容量更高、效能更好,還可與各種周邊設備和刺激互動。

AMD 為開發模擬與企業原型設計平台提供顯著優點,包括快速佈局與繞線功能可提升大型 ASIC 與特殊應用標準產品 (Application Specific Standard Parts, ASSP) 設計的生產力、完整的可見度除錯解決方案、降低系統層級耗電量,以及支援高使用率與 QoR 的類 ASIC 時脈功能和繞線結構。

AMD Vivado ML 實作工具

- 減少編譯時間

- 改善 QoR

- 特殊應用積體電路 (Application-Specific Integrated Circuit, ASIC) 式時脈功能,可有效對應複雜的 ASIC 與 SoC 時脈樹

高頻寬且低延遲的 I/O 和收發器

- FPGA 之間的高效率腳位多工功能

- 減少分區之間的延遲,改善系統效能

- 我們的 High-Speed Transceiver Pin Multiplexing IP 為業界提供支援

完整可見度除錯解決方案

- 具備可重入除錯探針修改功能,除錯週期短

- 完整的除錯可見度,支援配置型讀回、寫回和狀態擷取

- 透過 PCIe® 與深層儲存整合式邏輯分析器 (Integrated Logic Analyzer, ILA) 進行高速除錯,可將擷取資料卸載至外部記憶體

產品組合

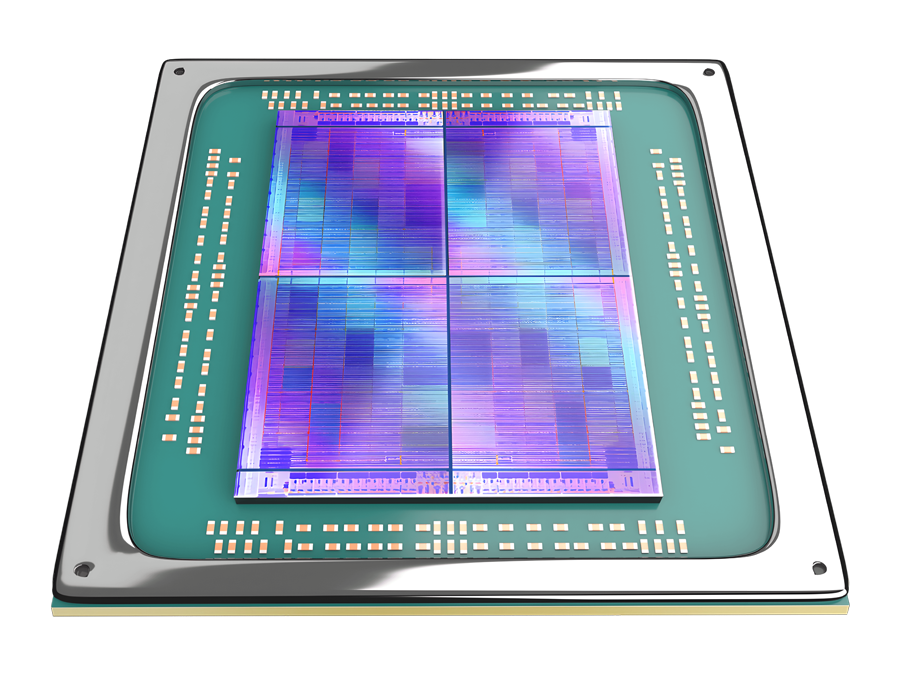

AMD Versal™ Premium VP1902 裝置:全球最大的自適應 SoC4

AMD Versal™ Premium VP1902 自適應 SoC 是第一款具有純量處理子系統單晶片的模擬級器件,能為軟體/硬體韌體開發和系統啟動支援多種控制和刺激產生使用模式。

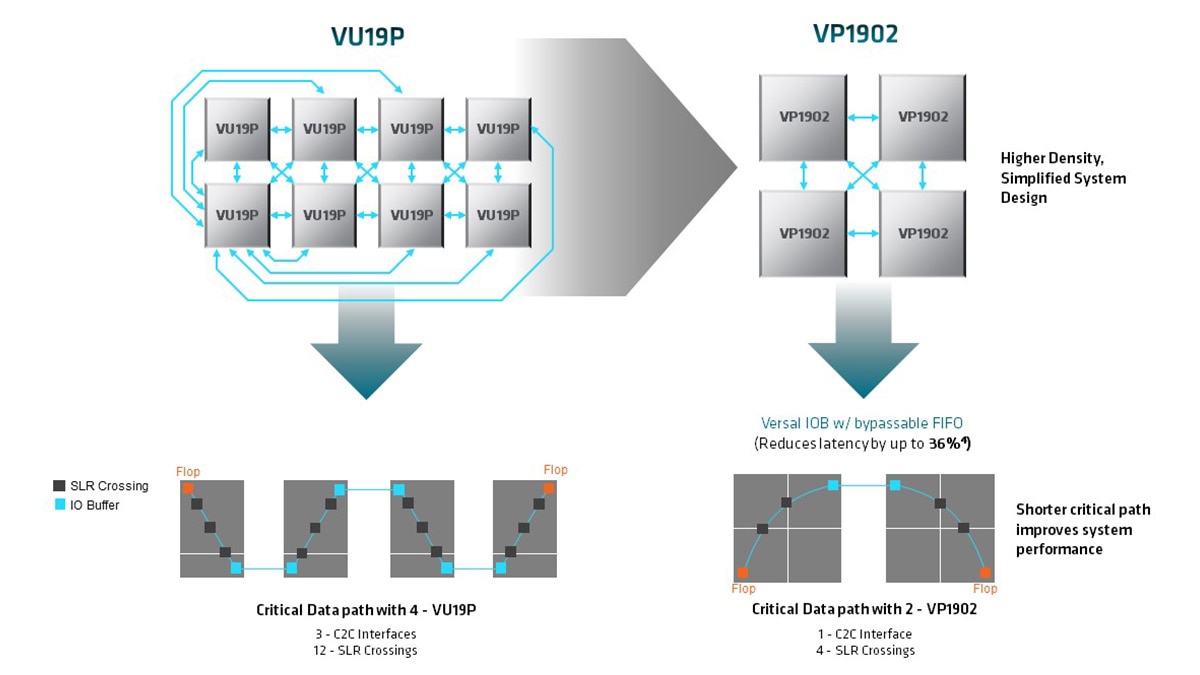

VP1902 裝置的裝置容量比 Virtex™ UltraScale+™ VU19P 裝置大一倍2,可適應更大的智財 (Intellectual Property, IP) 和設計子系統。晶片上 A72 Arm® 處理器可為軟硬體共同開發支援多種原型設計使用案例。我們的高性能輸入/輸出 (eXtreme Performance I/O, XPIO) 與 MIPI D-PHY 能支援多種高速周邊設備刺激。結合這些矽晶片的功能打造理想解決方案,滿足尖端 ASIC、IP 與 SoC 開發的原型設計需求。

精選 AMD 自適應運算合作夥伴

開始

使用 AMD Versal Premium 設計原型

AMD Versal™ Premium VP1902 裝置:全球最大的自適應 SoC

- 邏輯密度是 AMD Virtex™ UltraScale+™ VU19P 裝置的 2 倍2

- 可延展性強,提供 2 倍總 I/O 頻寬5 和 2.3 倍收發器頻寬6

- 減少 I/O 延遲且使用二乘二超級邏輯區域 (Super Logic Region, SLR) 陣列,改善系統效能

AMD VivadoTM ML 設計套裝

AMD Vivado™ ML 設計套裝具備用於改善編譯時間和成果品質 (Quality of Result, QoR) 的全新實作功能,可提供最先進的開發體驗。

支援與資源

聯絡銷售人員

我們的銷售團隊會根據您的特定需求,協助您做出最佳的技術決策。

尾註

- 根據 AMD 2023 年 5 月的內部分析。(VER-009)

- 根據 AMD 2023 年 5 月的內部分析,比較 Versal Premium VP1902 裝置與 Virtex UltraScale+ VU19P 裝置之間系統邏輯單元數量的差異。(VER-001)

- 根據 AMD 2023 年 5 月的內部系統時脈效能分析,比較 Versal Premium VP1902 裝置與 Virtex UltraScale+ VU19P 裝置在各種設計大小與切割網之間的差異。(VER-006)

- 根據 AMD 2023 年 5 月的內部分析,使用 6 輸入式查找表 (Look-Up Table, LUT),比較 Versal Premium VP1902 裝置與 Intel Stratix 10 GX 10M FPGA 之間的差異。(VER-002)

- 根據 AMD 實驗室測試,使用 A6865 套件執行模擬,比較 AMD Versal Premium VP1902 裝置 XPIO 資料率效能,與 AMD Virtex UltraScale+ VU19P FPGA 發佈資料率之間的差異。實際結果可能會有所不同。(VER-003)

- 根據 AMD 實驗室截至 2023 年 5 月為止的計算資料,比較 Versal Premium VP1902 裝置 B6865 套件的總收發器頻寬,與 Virtex UltraScale+ VU19P 裝置 B3824 套件之間的差異(假設 GTY/GTYP 以 32G 的速度執行,GTM 以 56G 的速度執行)。(VER-005)

尾註

- 根據 AMD 2023 年 5 月的內部分析。(VER-009)

- 根據 AMD 2023 年 5 月的內部分析,比較 Versal Premium VP1902 裝置與 Virtex UltraScale+ VU19P 裝置之間系統邏輯單元數量的差異。(VER-001)

- 根據 AMD 2023 年 5 月的內部系統時脈效能分析,比較 Versal Premium VP1902 裝置與 Virtex UltraScale+ VU19P 裝置在各種設計大小與切割網之間的差異。(VER-006)

- 根據 AMD 2023 年 5 月的內部分析,使用 6 輸入式查找表 (Look-Up Table, LUT),比較 Versal Premium VP1902 裝置與 Intel Stratix 10 GX 10M FPGA 之間的差異。(VER-002)

- 根據 AMD 實驗室測試,使用 A6865 套件執行模擬,比較 AMD Versal Premium VP1902 裝置 XPIO 資料率效能,與 AMD Virtex UltraScale+ VU19P FPGA 發佈資料率之間的差異。實際結果可能會有所不同。(VER-003)

- 根據 AMD 實驗室截至 2023 年 5 月為止的計算資料,比較 Versal Premium VP1902 裝置 B6865 套件的總收發器頻寬,與 Virtex UltraScale+ VU19P 裝置 B3824 套件之間的差異(假設 GTY/GTYP 以 32G 的速度執行,GTM 以 56G 的速度執行)。(VER-005)