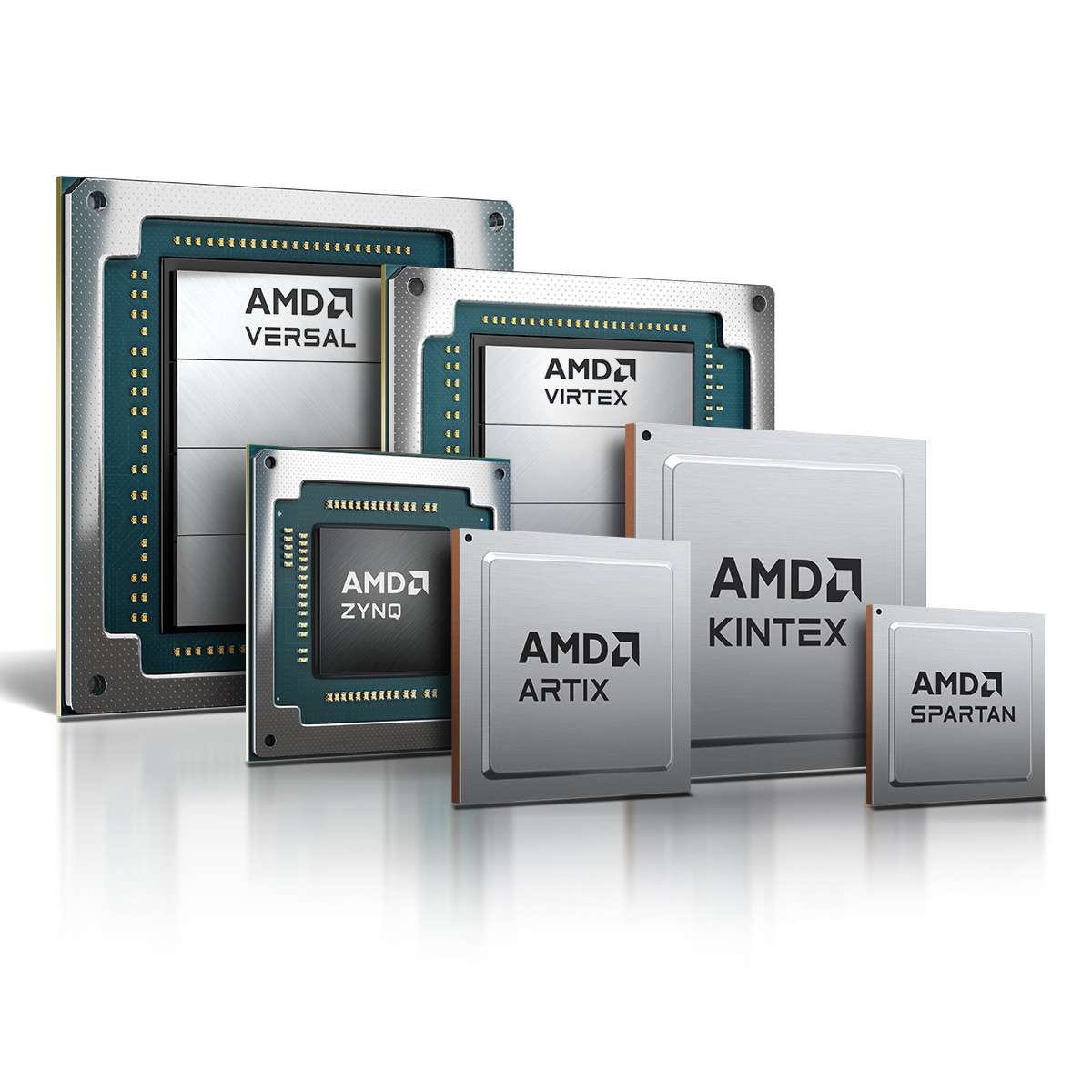

Der kostenlose paramaterisierbare Kern nutzt die seriellen I/O-Transceiver, die in Kintex™ UltraScale™, Virtex™ UltraScale™, Virtex 7, Kintex 7, Artix 7, Zynq™ 7000, Virtex 6, Virtex 5, Virtex 4 FX, Virtex II Pro und Spartan™ 6 zur Unterstützung der XAUI-Funktion verfügbar sind.

Die AMD 10 Gigabit Attachment Unit Interface (XAUI) LogiCORE™ IP bietet eine serielle High-Speed-Schnittstelle mit 4 Lanes für einen Gesamtdurchsatz von bis zu 10 Gigabit pro Sekunde (Gb/s). Der Kern arbeitet mit einer internen Taktfrequenz von 156,25 MHz und umfasst die XGMII Extender (DTE und PHY XGXS) sowie die Sublayer 10GBASE-X, wie in den Abschnitten 47 und 48 von IEEE 802.3-2012 beschrieben. Darüber hinaus unterstützt der Kern eine optionale serielle MDIO-Verwaltungsschnittstelle für den Zugriff auf die Verwaltungsregister nach IEEE 802.3-2012 Klausel 45. Die MDIO-Schnittstelle kann weggelassen werden, um Logik einzusparen. In diesem Fall wird eine vereinfachte Verwaltungsschnittstelle über Bitvektoren bereitgestellt.

Das Design entspricht der Norm IEEE 802.3ae-2012 und umfasst die folgenden Funktionen:

- 8B10B-Kodierung/Dekodierung mit Fehlererkennung

- Komma-Erkennung

- RX elastischer Puffer/Kanalbündelung

- Eine hochmoderne PMA (SERDES)

- Leer-Frame-Generierung bei Übertragung

- Synchronisierung Zustandsmaschine für jeden einzelnen Datenkanal

- Deskew (Taktflankenausrichtung) der Zustandsmaschine beim Empfang (Kanalbündelung)

- Vollständiger Satz von Verwaltungsregistern (gemäß IEEE 802.3ae-Spezifikationen)

Der XAUI-Kern ist ideal geeignet, um Hochleistungsverbindungstechnologien für Kommunikationsgeräte bereitzustellen und eine einfache Verbindung mit 10-Gbit/s-Transceivern zu ermöglichen, die diesen Standard unterstützen (z. B. XENPAK-kompatible Geräte).