XPS USB 2.0 Device

作者: AMD

使用此核心,AMD 通用序列匯流排 2.0 高速器件透過 32 位元處理器區域匯流排 (Processor Local Bus, PLB) 第 4.6 版,提供一個控制介面給內部暫存器,如 IBM® CoreConnect™ 128 位元處理器區域匯流排架構規格第 4.6 版所述。

- 零件編號:

- EF-DI-USB2-DEVICE-SITE

- 設計工具支援: ISE Design Suite

- 授權: Core License Agreement

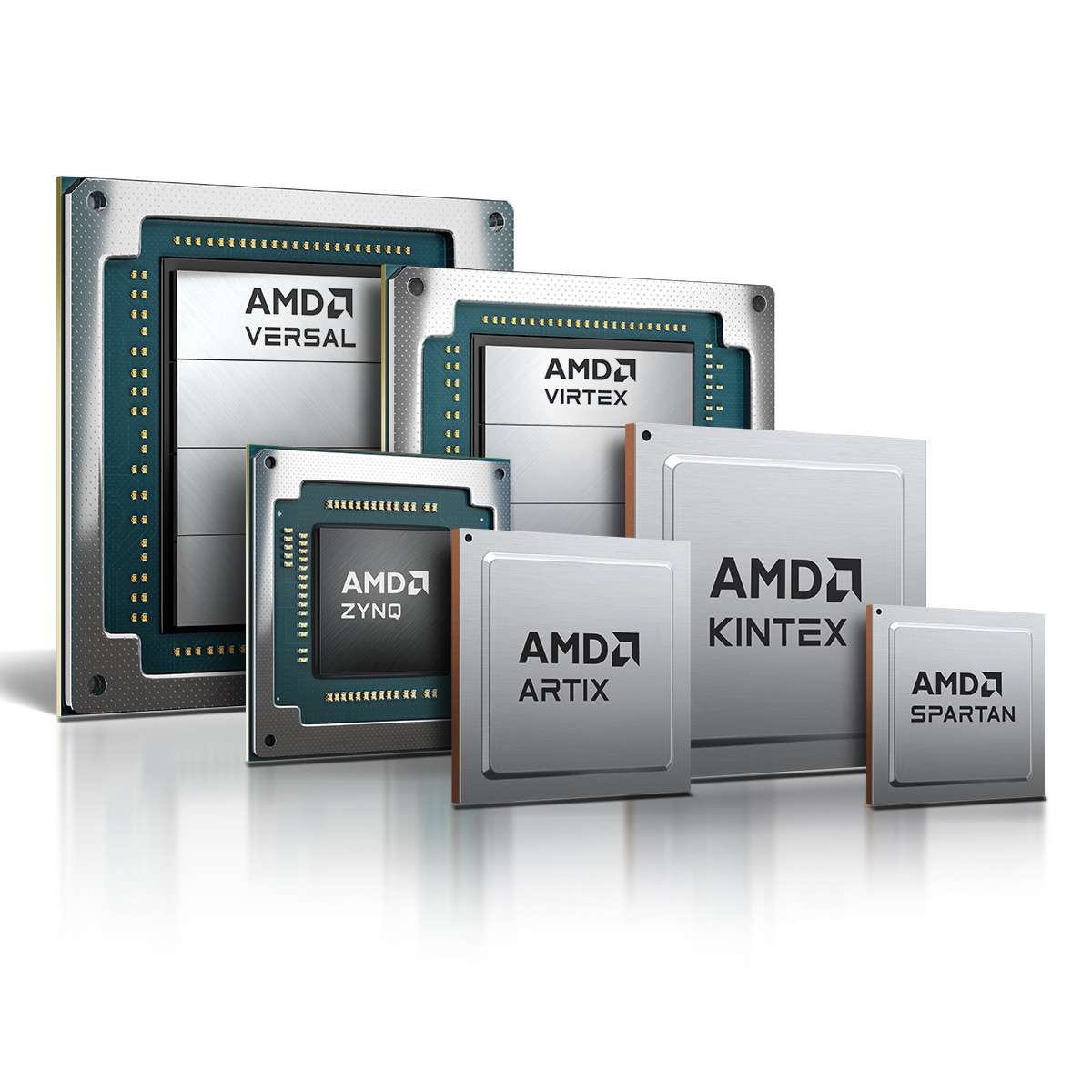

- 器件支援: Virtex 6, Spartan 6, Spartan 3E, Virtex 5, Spartan 3A, Spartan 3A DSP, Spartan 3, Virtex 4, Spartan 3AN