概述

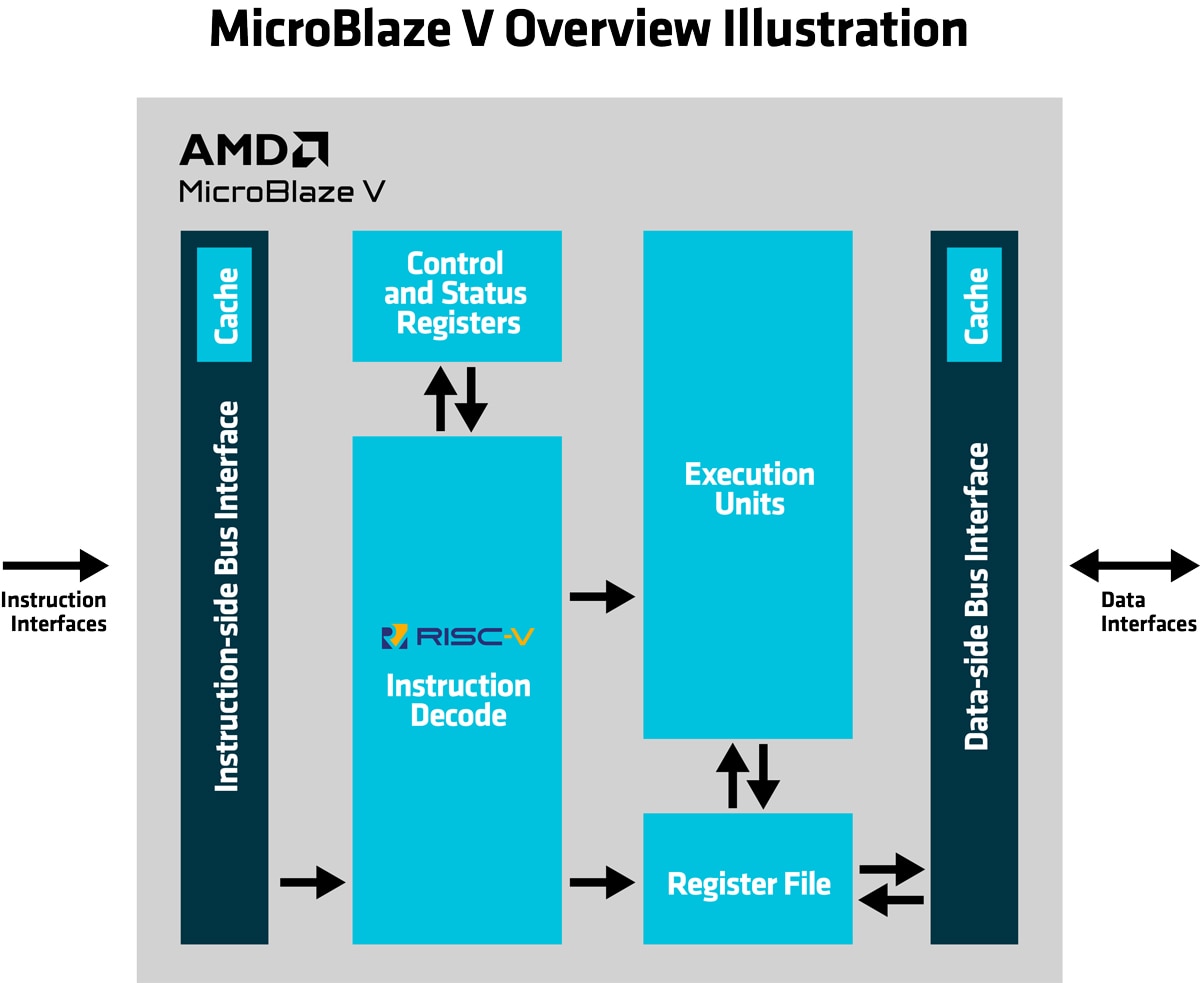

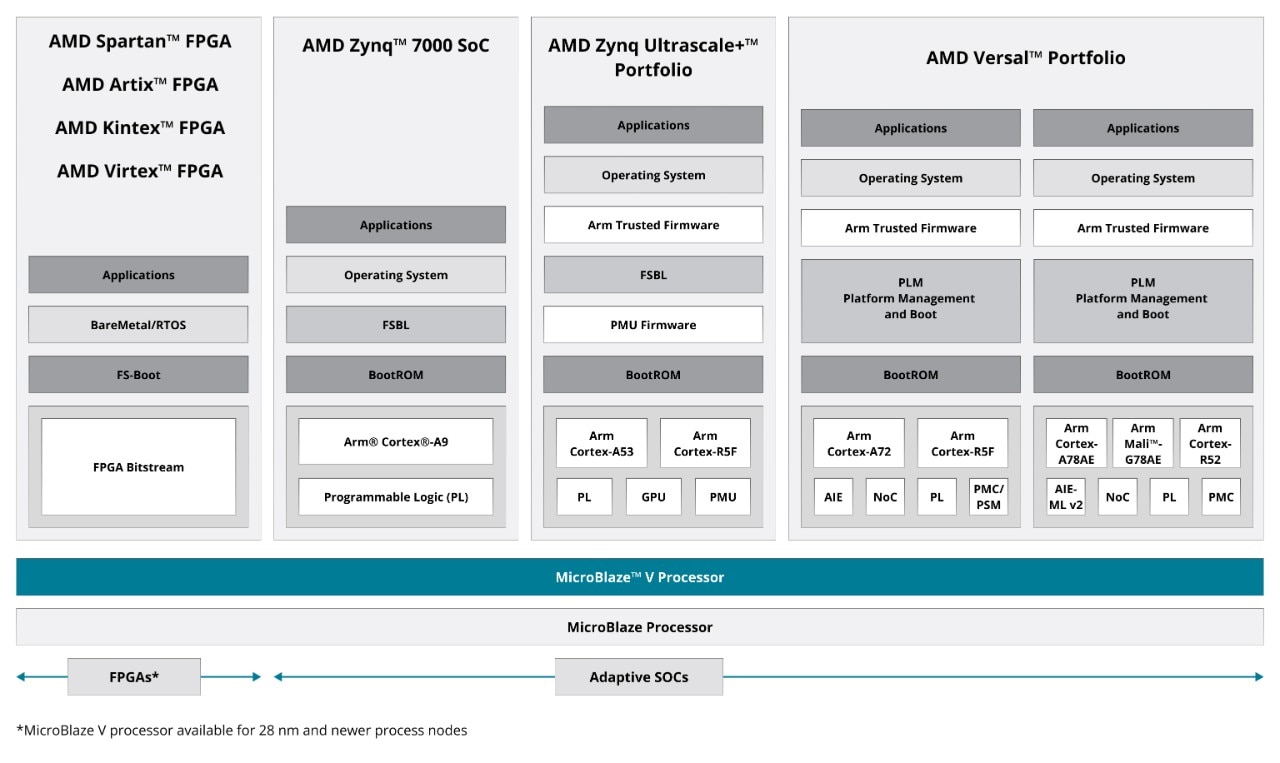

AMD MicroBlaze™ V 處理器是軟核 RISC-V 處理器 IP,適用於 AMD 自適應 SoC 和 FPGA。MicroBlaze V 處理器採用 RISC-V 指令集架構 (ISA) 為基礎。它不但讓開發人員能夠運用開放原始碼的 RISC-V 軟體生態系統,還能與傳統 MicroBlaze 處理器硬體相容,並且完全整合於 AMD Vivado™ 與 Vitis™ 工具的設計流程。AMD MicroBlaze V 處理器採用高度模組化設計,具適合嵌入式系統應用的可設定架構。

開發人員可將 MicroBlaze V 處理器應用於 Vivado Design Suite 所支援的任何特定 AMD 自適應 SoC 或 FPGA 器件,而不需額外費用。

RISC-V 是由非營利組織 RISC-V 基金會管理的開放原始碼標準指令集架構 (ISA)。AMD 自 2020 年開始即為會員。

關鍵功能

以 RISC-V 為基礎

開放原始碼 ISA

- 擁有遍及業界的完整軟體與解決方案生態系統作為後盾

- 可輕鬆對現有 MicroBlaze 處理器設計進行硬體移轉,並為 RISC-V 設計提供軟體可攜性

- 可配置的 ISA 支援 RV32I 和 RV64I 基本整數指令集,並提供以下選用指令集:

- 乘法與除法(「M」延伸)

- 原子指令(「A」延伸)

- 浮點(「F」延伸)

- 程式碼壓縮(「C」延伸)

- 位元運算(:B:、"ZBa"、"ZBB"、"ZBc"、"ZBs" 延伸)

- 提供程式碼壓縮,大幅減少程式碼大小並節省設計記憶體

高效率架核心構

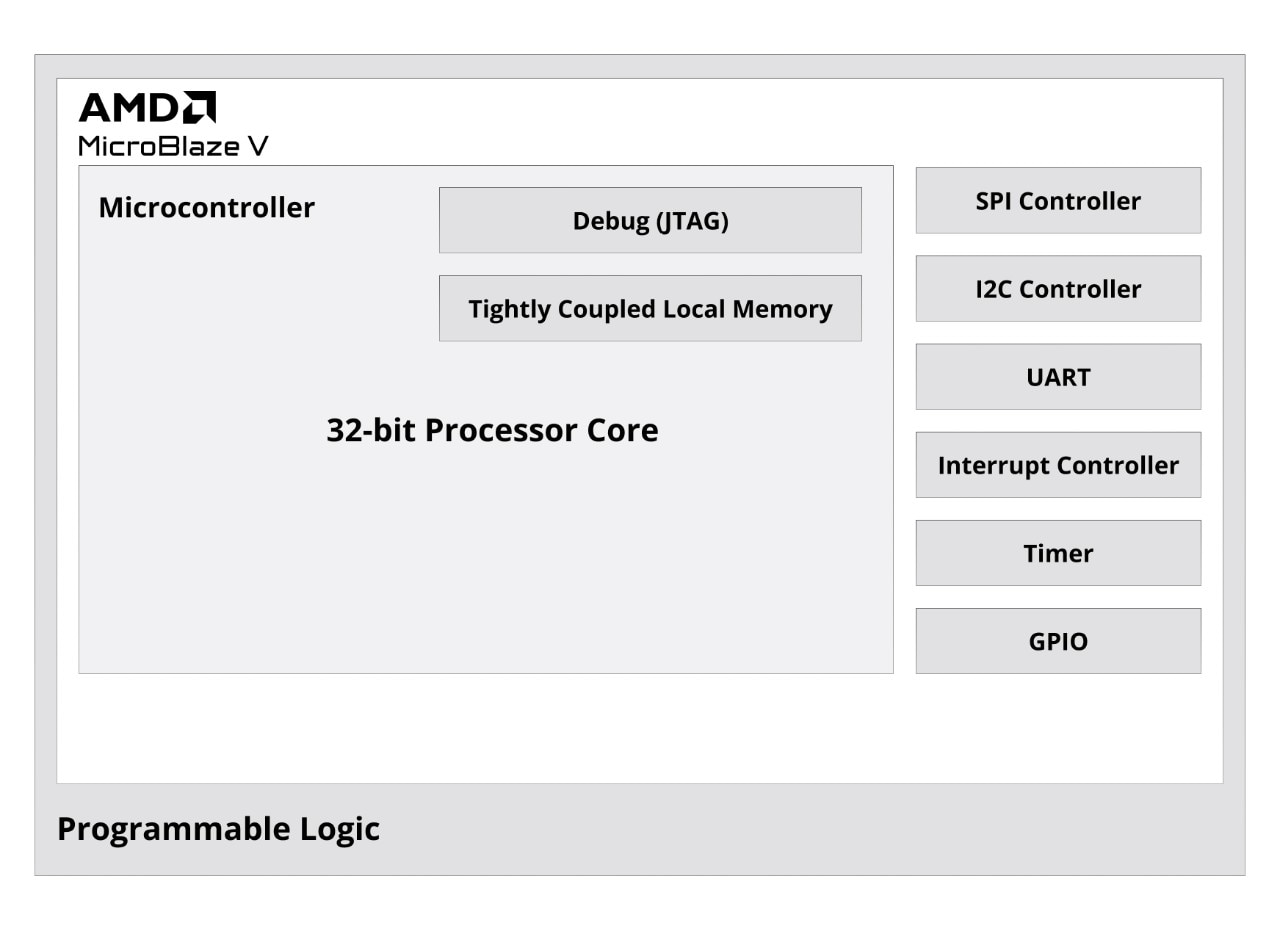

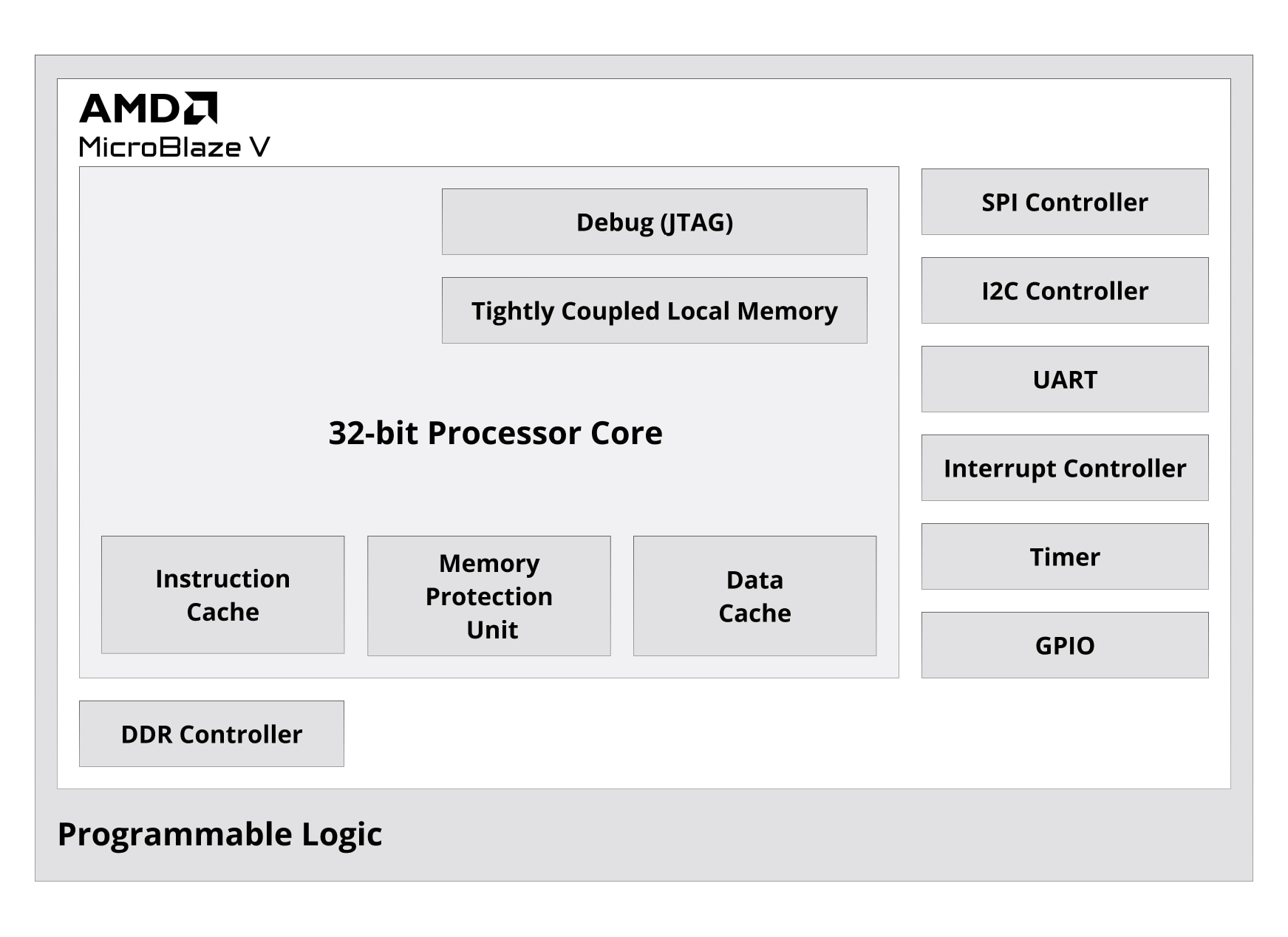

- 提供多種可選擇的預設配置,適合從微控制器到應用處理器等不同應用

- 提供四種管道選項,以最佳化區域及/或效能

- 可為首重安全的系統選擇納入安全措施,例如雙核心鎖步和三重模組冗餘 (TMR)

高度設計彈性

- 在 Vivado Design Suite 和 Vitis 軟體工具中提供完全整合的設計流程

- 相容於 Vivado 設計工具支援的所有 AMD 自適應 SoC 和 FPGA

- 透過圖形使用者介面 (GUI) 或命令列介面 (CLI) 提供友善的使用者體驗

- 透過多種最佳化 IP,減少在可程式化邏輯中部署整合式 MicroBlaze V 處理器子系統所需要的系統元件數量,並縮短開發時間

運用 AMD 經證實可靠且可信賴的 MicroBlaze™ 處理器。用途廣泛,效能穩定,是許多應用的可靠選擇。

處理器詳細資料

關鍵拖放式周邊設備

一般用途

- 多通道 DMA

- 串流 FIFO

- 計時器 / Watchdog

- 互斥鎖 / 信箱

I/O

- UART

- USB 2.0

- SPI

- GPIO

- PWM

影像

- HDMI 攝影機/顯示器介面

- MIPI-CSI、MIPI-DSI

- 視訊 DMA

記憶體

- DDR

- Quad SPI

- SDRAM

網路

- 乙太網路子系統

- 控制器區域網路

支援與資源

開始

MicroBlaze™ V 處理器已整合至 AMD Vivado™ 和 Vitis™,為使用者提供熟悉的設計流程。觀看網路研討會,通盤瞭解 MicroBlaze V 的各項功能及其優勢。

尾註

1.微控制器組態現已投入量產;配備 RV64I 與記憶體保護單元的 AMD MicroBlaze V 目前處於搶先體驗階段;配備記憶體管理單元的 AMD MicroBlaze V 則尚在發展藍圖階段。

尾註

1.微控制器組態現已投入量產;配備 RV64I 與記憶體保護單元的 AMD MicroBlaze V 目前處於搶先體驗階段;配備記憶體管理單元的 AMD MicroBlaze V 則尚在發展藍圖階段。