AMD präsentiert PAM4-fähige Virtex™ UltraScale+™ FPGAs

Wir zeigen Ihnen, wie AMD PAM4-Transceiver mit 58 Gb/s in das 16 nm Virtex™ UltraScale+™-Portfolio integriert hat. Die neuen Virtex UltraScale+ FPGAs, basierend auf branchenführenden High-End-FPGAs, verdoppeln die Bandbreite bestehender Infrastrukturen für Anwendungen in den Bereichen Data Center Interconnect, 5G-Infrastruktur und Networking, Test- und Messanwendungen sowie Luft- und Raumfahrt und Verteidigung. Sie ermöglichen eine nahtlose Migration bestehender Systeme zu modernen Rückplane-, Optik- und Hochleistungs-Interconnect-Lösungen.

AMD Virtex™ UltraScale+™ 58G – Produktvorteile

Um die nächste Welle der Ethernet-Einführung voranzutreiben, integriert AMD 58-Gb/s-Transceiver in die 16 nm FinFET+ Virtex UltraScale+ FPGA-Familie.

Die AMD Virtex UltraScale+ 58G PAM4 FPGAs verdoppeln die Bandbreite auf der vorhandenen Infrastruktur und verlängern die ASIC-Lebensdauer. Diese FPGAs bieten die schnellsten Transceiver in einem hardwareprogrammierbaren Chip mit neuer optischer Verfügbarkeit und ermöglichen es Benutzern, zukunftssichere Systeme zu bauen.

Hauptfunktionen und Vorteile

Schnellste Transceiver

Bis zu 48 Transceiver mit bis zu 58 Gb/s PAM4 für Multi-Terabit-Systeme und bis zu 32 Transceiver mit 32,75 Gb/s für 25G-Interoperabilität

Flexible Konnektivität

28G- und 58G-Backplanes, 32,75 Gb/s und 58 Gb/s Chip-to-Chip und Chip-to-Optics-Unterstützung

Hervorragende Signalintegrität

Überlegene Signalintegrität für 50/100/200/400G-Optik und -Protokolle über eine verbesserte kontinuierliche adaptive RX-Entzerrung und integrierte KR-FEC

Erweiterte DSP-Kerne

Bis zu 38 TOPs (22 TeraMACs) DSP-Rechenleistung für verschiedene Anwendungen im Rechenzentrum

Reduzierter Platzbedarf

Eliminierung einzelner ICs für Ethernet, Gearboxes, Speicher und PCIe – Integration dieser Funktionen in einem einzigen Chip für kompaktere Systemgestaltung bei gleichbleibender Leistung

Integrierter Block für PCI Express

PCIe® Gen3x16 in allen Geräten und PCIe Gen4x8 mit CCIX-Unterstützung in ausgewählten Geräten ermöglichen komplette End-to-End-Lösungen, die Multi-100G Portsy unterstützen.

Portfolio

Wir stellen vor: Die Virtex UltraScale+ Familie

Anwendungen

Neue Möglichkeiten mit Virtex UltraScale+ 58G PAM4 FPGAs

U-Bahn- und Transportnetzwerke

Aufgrund der rapide steigenden Bandbreitenanforderungen im 5G-Bereich stehen PON-, Kabelzugangs-, U-Bahn- und Verkehrsnetze unter enormem Druck, den aggregierten Netzwerkverkehr effizient an die Kernnetze zu liefern. Virtex UltraScale+ 58G FPGAs bieten 58G PAM4-Transceiver mit dediziertem 100G MAC IP, damit Entwickler flexible Geräte mit höherer Portdichte und höherem Durchsatz bauen können. Dank der Programmierbarkeit ermöglichen Virtex UltraScale+ 58G PAM4 FPGAs benutzerdefinierte Logik und die Möglichkeit, KI/ML für intelligente Transportnetze hinzuzufügen, sodass sich Anbieter von Netzwerkgeräten (NEPs) auf die Innovation und Differenzierung von Endprodukten konzentrieren können und gleichzeitig die Markteinführungszeit und die Gesamtbetriebskosten reduzieren.

Netzwerktestgeräte

Signalanalysegeräte wie Spektrum-/Netzwerkanalysatoren erfordern eine höhere Signalverarbeitungsleistung und eine hohe E/A-Bandbreite. Die Virtex UltraScale+ 58G PAM4 FPGAs bieten UltraRAM für die Datenpufferung und Block-RAM für Koeffiziententabellen und FIFOs. Mit einer beträchtlichen Anzahl von DSP-Blöcken und 80 Hochgeschwindigkeits-Transceivern, die im FPGA verfügbar sind, können Entwickler von Test- und Messplattformen ein flexibles und skalierbares Hochleistungssystem aufbauen.

Smart Network Interface Card (SmartNIC)

Durch die Integration von PAM4-Transceivern in die Virtex UltraScale+ 58G Pam4 FPGAs können SmartNIC-Designer Gearboxes eliminieren und ihre Designs vereinfachen. Die PCIe Gen4-Unterstützung erhöht die Datenverarbeitungskapazität eines Servers erheblich und verbessert die Leistung, indem sie Beschleunigungsfunktionen bietet und gleichzeitig E/A-Engpässe beseitigt. Darüber hinaus umfassen FPGAs eine große Palette an Workloads, sodass SmartNICs, die mit Virtex UltraScale+ 58G PAM4 FPGAs erstellt wurden, Workloads über Rechen-, Netzwerk- und Speichersysteme hinweg hinzufügen und kombinieren können, wodurch die Funktionalität dynamisch geändert wird, ohne die Konnektivität zu beeinträchtigen.

Data Center Interconnect (DCI)

Wenn Rechenzentren skalieren, müssen DCI-Technologien (Data Center Interconnect, Verbindungen zwischen Rechenzentren) entwickelt werden, um hohe Kapazität, Skalierbarkeit und Energieeffizienz zu ermöglichen. Um der Nachfrage nach Hochleistungskonnektivität zwischen Rechenzentren gerecht zu werden, bieten Virtex UltraScale+ 58G PAM4 FPGAs einen schnellen E/A-Durchsatz, indem sie die neue Optik und Protokolle mit überlegener Portdichte und Performance/Watt unterstützen.

Fronthaul-Gateways für konvergierten Zugriff

Fronthaul-Gateways für konvergierten Zugriff sind einer der Schlüssel für eine kosteneffiziente 5G-Erweiterung und Servicebereitstellung. Dank der Programmierbarkeit von Virtex UltraScale+ FPGAs können diese Gateways mehrere Funktionen bedienen und ermöglichen die Übertragung mehrerer Dienste über eine einzige Schnittstelle wie Ethernet, FlexE und optische Transportnetzwerke (OTNs). Mit 58G PAM4-Transceivern unterstützen Fronthaul-Gateways Multi-100G-Schnittstellen mit neuer Optik zur Optimierung der Transportkosten. Die Virtex UltraScale+ 58G PAM4 FPGAs bieten den Weg zu einer einzigen, vereinheitlichten Gateway-Funktion für Dienstanbieter, die Kosten sparen und ihrer sich entwickelnden 4G- und 5G-Zugangsinfrastruktur erhebliche Flexibilität hinzufügen möchten.

Speicherbeschleunigung

Die explosionsartige Erhöhung der Datenmenge in modernen Anwendungen belastet die Speicherinfrastruktur, wobei die Bandbreitenanforderungen schnell steigen, während die Anforderungen an Leistung und Formfaktor konstant bleiben. Für Speichersysteme der nächsten Generation eignen sich FPGAs ideal für die Bereitstellung verbesserter Performance in Systemen mit RDMA- und NVMe-over-Fabrics (NVMe-of)-Offloads, die entweder als SSD-Controller oder in hyperkonvergente Infrastruktur integriert sind, um komplexe Speicherverarbeitungsaufgaben zu bewältigen. Mit integrierten 58G-PAM4-Transceivern, kompakten Gehäuseoptionen und PCIe-Gen4-IP ermöglichen die Virtex UltraScale+ 58G-PAM4-FPGAs eine beschleunigte Verarbeitung verschiedenster Speicher-Workloads wie Datenkomprimierung, -dekomprimierung, Deduplizierung oder Sequenzierung. Dabei verbessern sie die Gesamtspeicherauslastung und entlasten die CPU.

Produkttabelle

| XCVU23P | XCVU27P | XCVU29P | |

|---|---|---|---|

| Systemlogikzellen (in Tausend) |

2.252 | 2.835 | 3.780 |

| DSP-Schichten | 1.320 | 9.216 | 12.288 |

| Speicher (Mb) | 173 | 341 | 455 |

| GTY/GTM-Transceiver (32,75/58 Gb/s) |

34/4 | 32/48 | 32/48 |

| HP E/A | 572 | 676 | 676 |

Erste Schritte

Starten Sie direkt Ihren Designzyklus und erzielen Sie eine schnelle Markteinführung mit bewährter Hardware, Software-Support, Tools, Konzeptbeispielen und für das Kit verfügbarer Dokumentation.

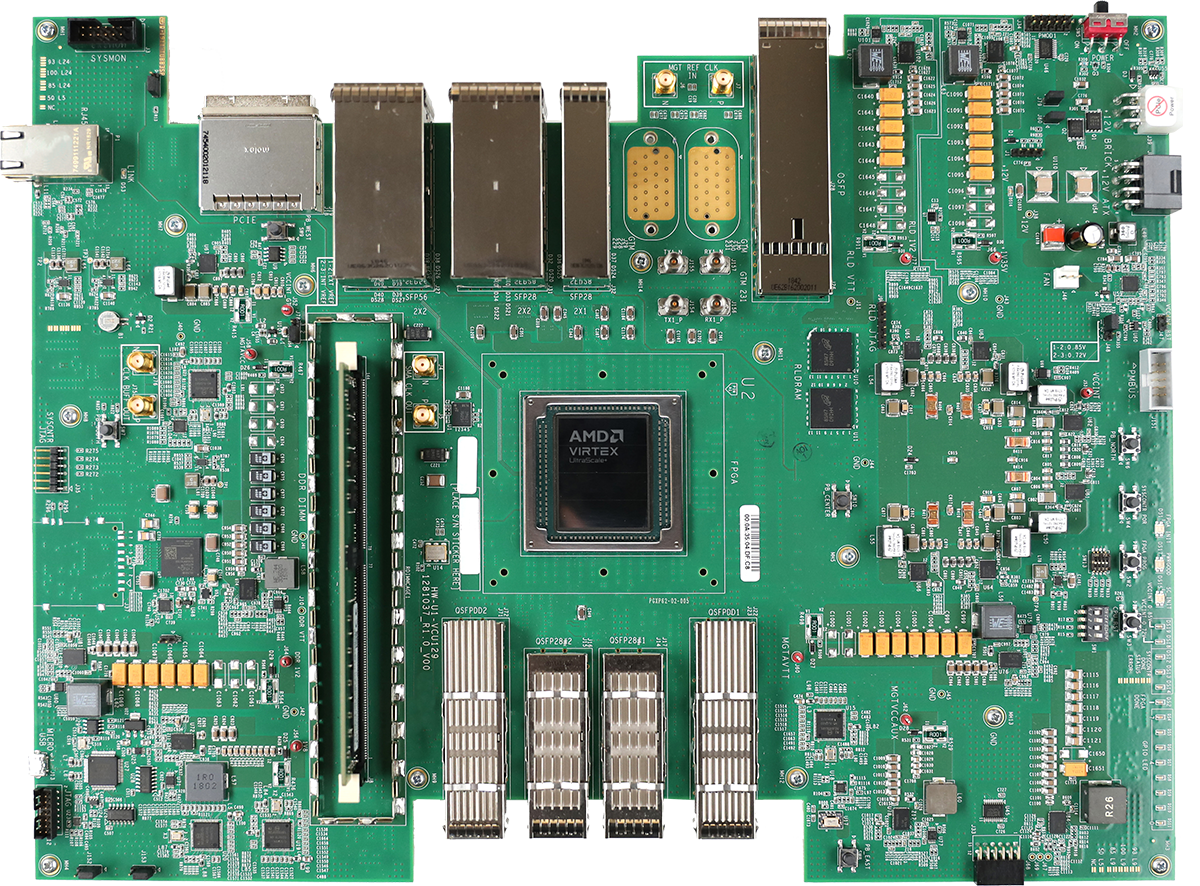

Virtex UltraScale+ 56G PAM4 VCU129 FPGA – Evaluierungskit

Das Virtex UltraScale+ 56G PAM4 VCU129 FPGA-Evaluierungskit ist ideal für die Evaluierung und das Prototyping von Ethernet der nächsten Generation und anderen 50G+-Schnittstellen, die durch die AMD 58G PAM4 Transceiver-Technologie im VU29P FPGA unterstützt werden.

Unterstützung und Ressourcen

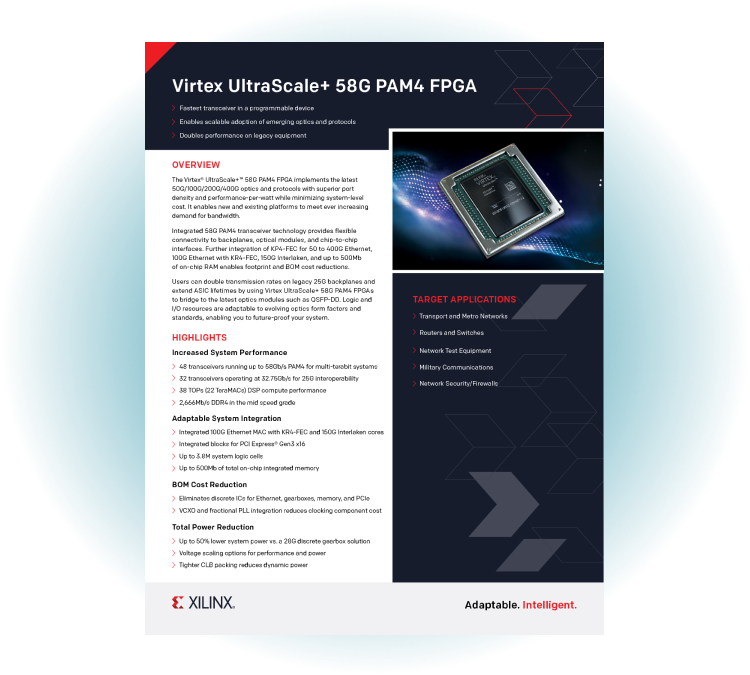

Virtex UltraScale+ 58G PAM4 FPGA – Produktübersicht

Das Virtex UltraScale+ 58G PAM4 FPGA unterstützt die neuesten 50G/100G/200G/400G-Optiken und -Protokolle und bietet herausragende Portdichte sowie höchste Performance/Watt – bei gleichzeitig optimierten Systemkosten.

Vertrieb kontaktieren

Unser Vertriebsteam unterstützt Sie bei der Auswahl der besten Technologien für Ihre spezifischen Anforderungen.