AMD Virtex™ UltraScale+™ 58G 製品の特長

次世代のイーサネット運用をサポートするため、AMD は 16 nm FinFET+ を採用した Virtex UltraScale+ FPGA ファミリに 58 Gb/s トランシーバーを統合しました。

AMD Virtex + 58G PAM4 FPGA は、既存インフラの帯域幅を 2 倍にし、ASIC の寿命を延長します。ハードウェア プログラマブルなデバイスに最速トランシーバーを搭載したこの FPGA は、最新の光技術だけでなく、将来的な要件にも対応するシステムを構築できます。

主な機能と利点

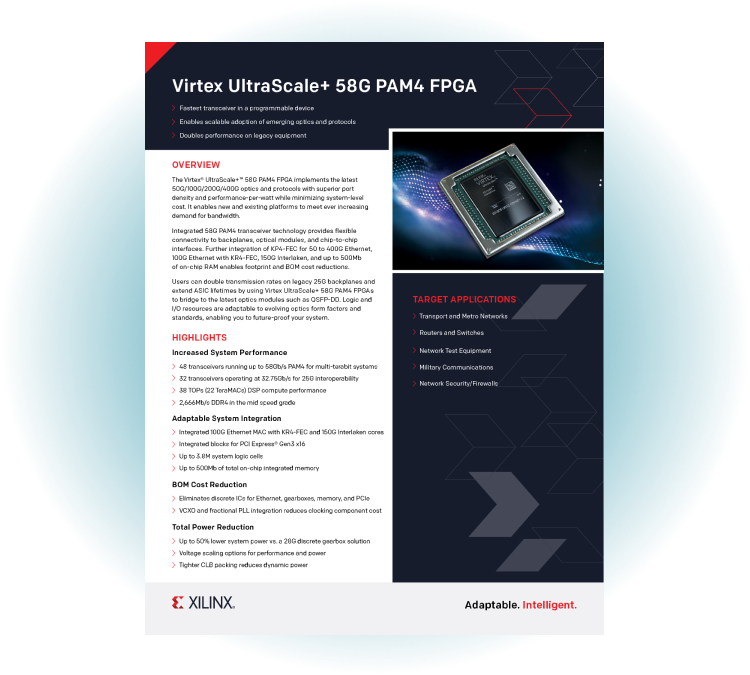

最速トランシーバー

マルチテラビット システムに対応する最大 58 Gb/s PAM4 で動作する最大 48 個のトランシーバーと、25G のインターオペラビリティ向けに 32.75 Gb/s で動作する 32 個のトランシーバー

柔軟なコネクティビティ

バックプレーンは 28G/58G、32.75 Gb/s および 58 Gb/s のチップ間接続、チップと光ファイバーの接続に対応

優れたシグナル インテグリティ

強化された連続適応型 RX イコライゼーションと内蔵の KR-FEC による、50/100/200/400G 光通信/プロトコル向けの高品質な高速信号

強化された DSP コア

データセンターの多様なアプリケーションに対応する最大 38TOPs (22 TeraMACs) の DSP 演算性能

フットプリント削減

イーサネット、ギアボックス、メモリ、および PCIe 用のディスクリート回路が不要になるため、性能はそのままで小型フットプリントでのシステム設計が可能

PCI Express 用統合ブロック

すべてのデバイスに PCIe® Gen3x16 を搭載し、一部のデバイスでは CCIX に対応した PCIe Gen4x8 をサポートすることで、マルチ 100G ポートに対応した完全なエンドツーエンド ソリューションを実現

製品ポートフォリオ

Virtex UltraScale+ ファミリを紹介

アプリケーション

Virtex UltraScale+ 58G PAM4 FPGA がもたらす新たな可能性を探る

メトロ/トランスポート ネットワーク

5G、PON、ケーブル アクセス、およびメトロ/トランスポート ネットワークに対応する広帯域化ニーズが急速に高まっているため、ネットワーク トラフィックをコア ネットワークへ集約する必要性が生じています。Virtex UltraScale+ 58G FPGA は、専用の 100G MAC IP を使用する 58G PAM4 トランシーバーを搭載しているため、高密度ポートでより高いスループットを達成する柔軟なシステムを構築できます。プログラム可能な Virtex UltraScale+ 58G PAM4 FPGA では、独自のロジックを構築でき、スマート トランスポート ネットワーク向けの AI/ML 機能を追加できるため、ネットワーク機器プロバイダー (NEP) は革新的な差別化製品を完成させることに注力できる上に、設計期間の短縮と総保有コスト (TCO) の削減も可能になります。

ネットワーク テスト装置

スペクトラム/ネットワーク アナライザーなどの信号解析装置には、より高度な信号処理能力と広い I/O 帯域幅が必要です。Virtex UltraScale+ 58G PAM4 FPGA は、データ格納用の UltraRAM と、係数テーブル/ FIFO 用のブロック RAM を提供します。また、多数の DSP ブロックと 80 個の高速トランシーバーを搭載しているため、テスト/計測機器プラットフォームの設計者は、柔軟性と拡張性がある高性能システムを構築できます。

スマート NIC (Network Interface Card)

Virtex UltraScale+ 58G PAM4 FPGA に統合された PAM4 トランシーバーを使用することで、ギアボックスが不要になりシンプルな設計が可能になります。PCIe Gen4 に対応しているため、サーバーのデータ処理能力が劇的に向上し、アクセラレーション機能を提供することでさらに性能強化しながら I/O ボトルネックを軽減させることが可能です。さらに、FPGA は多様なワークロードに対応できることから、Virtex UltraScale+ 58G PAM4 FPGA を搭載した SmartNIC は、コネクティビティを犠牲にすることなく機能を動的にシフトして、計算、ネットワーク、ストレージにおいてワークロードを追加したり、組み合わせることが可能になります。

データセンター インターコネクト(DCI)

データセンターの規模が大きくなるにつれて、データセンター間の相互接続通信技術を進化させて、大容量、優れた拡張性、高い電力効率を実現する必要があります。Virtex UltraScale+ 58G PAM4 FPGA は、データセンター間の高性能な接続要件に応えるため、高いポート密度と優れたワットあたり性能で最新の光通信/プロトコルをサポートし、高い I/O スループットを実現します。

コンバージド アクセス フロントホール ゲートウェイ

コンバージド アクセス フロントホール ゲートウェイは、5G のシステム構築およびサービス提供を可能にする費用対効果に優れた方法の 1 つです。プログラマビリティを備えた Virtex UltraScale+ FPGA を使用することで、これらのゲートウェイは複数機能に対応できるようになり、イーサネット、FlexE、光トランスポート ネットワーク (OTN) などの単一のインターフェイスで複数のサービスを実行できます。58G PAM4 トランシーバーを備えたフロントホールゲートウェイは、最新の光技術で数百ギガレベルのインターフェイスをサポートし、 トランスポートのコストを削減します。Virtex UltraScale+ 58G PAM4 FPGA は、コストを抑えながら最新の 4G/5G アクセス ネットワークに対応する優れた柔軟性を提供できるため、単一のコンバージド ゲートウェイ機能を実現するのに最適なソリューションです。

ストレージ アクセラレーション

アプリケーションの進化によってデータ量が爆発的に増加し、ストレージ インフラに大きな負荷がかかるようになりました。そこで消費電力やフォームファクターを犠牲にすることなく広帯域化を実現するニーズが高まっています。次世代ストレージ システムの構築には、RDMA や NVMe-oF (NVMe over Fabrics) オフロード機能でシステム性能を向上させることができる FPGA が最適なソリューションです。SSD コントローラーとして統合したり、ストレージの複雑な処理タスクに対応するハイパーコンバージド インフラストラクチャを構築して性能を向上させることが可能です。58G PAM4 トランシーバー、小規模パッケージ オプション、PCIe Gen4 IP を備える Virtex UltraScale+ FPGA は、データの圧縮/解凍、重複排除、シーケンサー機能など、さまざまなタイプのストレージ ワークロードを高速化するのに有効である上に、ストレージ全体の使用率を改善し、CPU の負担を軽減させることも可能です。

製品一覧

| XCVU23P | XCVU27P | XCVU29P | |

|---|---|---|---|

| システム ロジック セル (K) |

2,252 | 2,835 | 3,780 |

| DSP スライス | 1,320 | 9,216 | 12,288 |

| メモリ (Mb) | 173 | 341 | 455 |

| GTY/GTM トランシーバー (32.75/58 Gb/s) |

34/4 | 32/48 | 32/48 |

| HP I/O | 572 | 676 | 676 |

利用開始

実証済みの HW/SW サポート、ツール、デザイン サンプル、およびキットに対応した関連資料を利用することで、すぐに設計を開始して製品の市場投入までの期間を短縮できます。

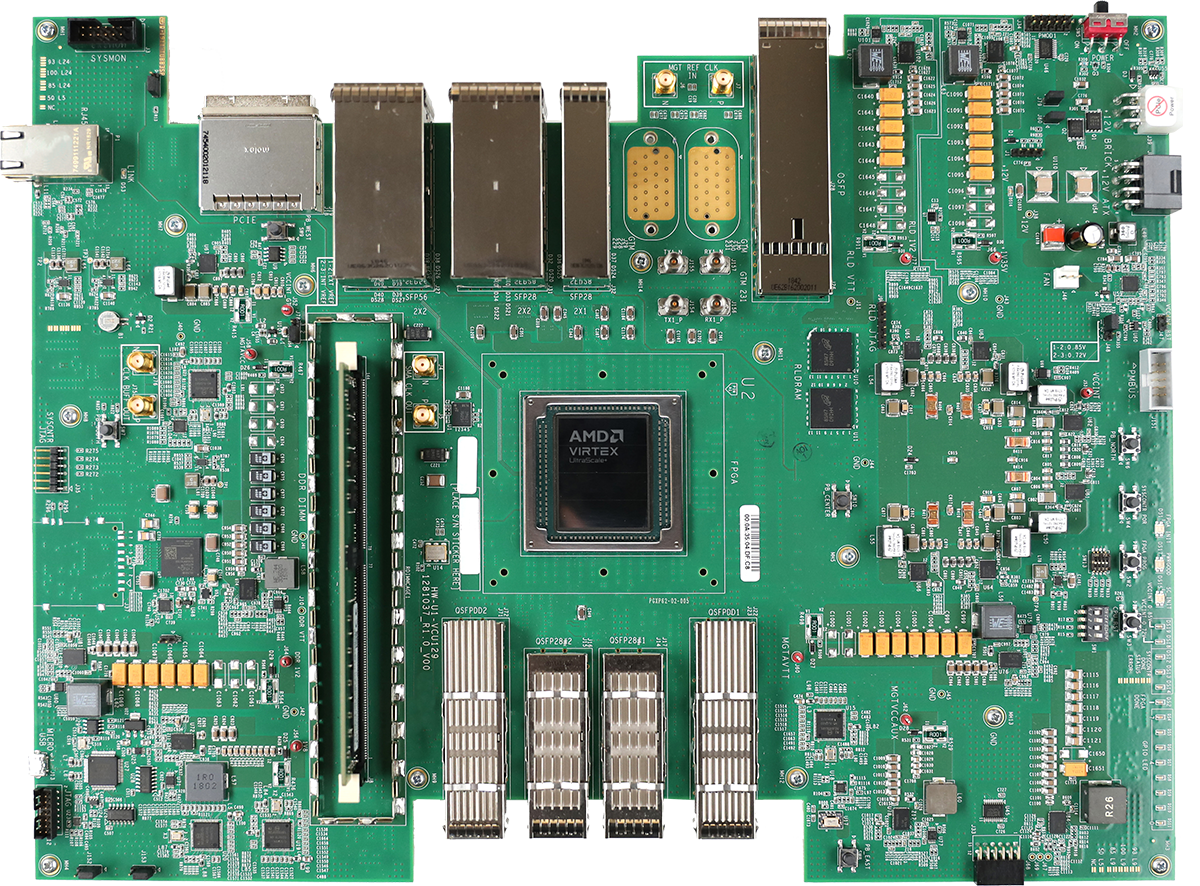

Virtex UltraScale+ 56G PAM4 VCU129 FPGA 評価キット

Virtex UltraScale+ 56G PAM4 VCU129 FPGA 評価キットは、VU29P FPGA に搭載されている AMD 58G PAM4 トランシーバー テクノロジを利用した次世代イーサネットおよびその他の 50G+ インターフェイスの評価およびプロトタイピングに最適です。

サポートとリソース

Virtex UltraScale+ 58G PAM4 FPGA 製品パンフレット

Virtex UltraScale+58G PAM4 FPGA は、システム レベルのコストを最小限に抑えながら、高いポート密度とワットあたり性能を備えた最新の 50G/100G/200G/400G 光通信技術およびプロトコルを実装しています。

営業に問い合わせ

AMD のセールス チームがお客様のニーズに合ったベストな技術的判断ができるようお手伝いいたします。