AMD Spartan UltraScale+ FPGA

- 採用 28 nm 與更小製程技術製造的 FPGA,有著業界最高的 I/O 對邏輯單元比3

- 與前一代產品相比,總耗電量最高可降低 30%9

高效率的矽晶,簡單易用的工具,廣大的開發生態系統。

更高的價值。縮短上市時間。更低的解決方案總成本。1

解決方案總成本不是只有晶片這一項。真正成本最佳化的 FPGA 解決方案會考慮到架構效率、封裝特性、設計工具成本與可用性、IP 授權與整合、開發心力等項目。

我們從最先進的晶片開始,滿足您對效能與功率規格的需求。我們經實證的按鈕式工具可簡化設計流程,並提供產品快速上市所需要的彈性。AMD 擁有業界最大的合作夥伴與 IP 生態系統支援,可協助您在競爭中保持領先。2

瞭解 AMD 如何從開始到結束,一路領先群倫。

加速實現從汽車、工廠再到雲端的創新。

透過業界最大開發生態系統,更快打造解決方案。2

與信賴的合作夥伴一起發揮實際影響力,同時降低解決方案總成本。

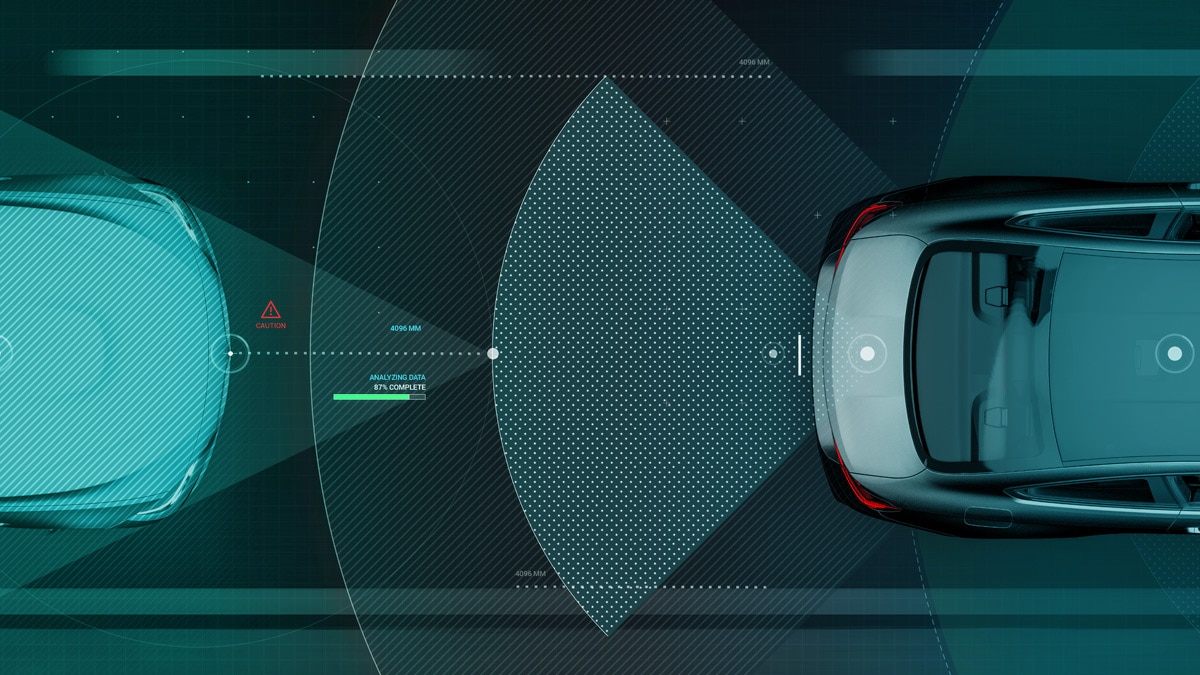

運用長波紅外線 (LWIR) 鏡頭節能且即時的影像處理能力,增強夜視、行人偵測和自動緊急煞車 (AEB) 等功能。透過 AMD 廣大的汽車 IP 生態系統(包括 Stradvision、Xylon 和 Makarena 等合作夥伴),簡化散熱管理並加快打入市場速度。

瞭解能效、精巧外型規格,以及重要的安全與安全性功能如何為 LWIR 鏡頭實現更快速的影像感測器處理和即時響應速度。

AMD FPGA 可提供精巧、節能的即時影像處理功能,並簡化散熱管理。存取開放原始碼程式庫、超過 250 個免費 AMD Vivado™ IP 核心、超過 700 個 Vitis™ 功能,和免費 MicroBlaze™ V 處理器,以快速開發和部署採用 AI 技術的機器視覺解決方案。

AMD FPGA 與自適應 SoC 產品組合可提供低成本解決方案,同時還可支援現今快步調生產線所需的最新感測器與輸出介面。

適用於機器人和工廠自動化的節能 FPGA 與 SoC 解決方案可提高生產力。透過 AMD 時間敏感網路 IP,將自主機器人的邊緣智慧極大化、簡化散熱管理,以及加速開發。

瞭解 AMD 如何實現高效率致動器控制、高速資料擷取和低功耗影像處理。

AMD 成本最佳化 FPGA 與自適應 SoC 可提供領先業界的每邏輯單元 I/O 比例3,提高機架使用效率和改善 TCO,適合用來擴充智慧型伺服器與資料中心基板管理控制器 (BMC) 解決方案。透過 AMD 健全的生態系統和 AMD EPYC™ 處理器參考設計,加速 BMC 整合。

透過適用於 PQC 演算法的內建安全性、符合 OCP 規範 (DC-SCM 2.1) 的互通性,以及 AMD Vivado Design Suite 所提供的快速開發流程,這些解決方案可為智慧型資料中心實現快速、安全且可擴充的 BMC 部署。

AMD 成本最佳化 FPGA 與自適應 SoC 可為 Pro AV 提供高頻寬、低功耗的解決方案,以精巧設計實現流暢的 PCIe® Gen4 視訊擷取、處理和 4K 播放。先進的 I/O、整合式記憶體控制器和多樣化視訊介面支援,使其非常適合新一代專業影音系統。

AMD Spartan UltraScale+ FPGA 配備高速 16.3 Gb/s 收發器、內建外部記憶體控制器和 PCIe Gen4 介面支援,可實現 AV-over-IP 網路橋接器、視訊轉換器,以及 PCIe 擷取卡、播放卡與處理卡這類的專業 AV 與廣播應用。

使用 Spartan UltraScale+ FPGAs 完成更多。尖端網狀架構、頂尖的周邊設備,以及優異的散熱封裝4,為您的成本敏感應用提供領先業界的效能5。尋找最適合您目前與未來需求的器件。

相較於競爭對手的 LUT4 架構6,LUT6 的平均使用率提高了 40%,因為高效率的設計始於高效率的架構!

在最高速度等級下使用相同 16 nm 製程節點,FMAX 比競爭對手平均高出 1.8 倍。5

相較於競爭對手的 LUT4 架構,Spartan UltraScale+ FPGA 的 LUT6 架構,以及高效能設計的先進封裝最高可降低 46% 總耗電量。7

節省寶貴時間。消除不必要的反覆運算,並避免下載額外工具。Vivado Design Suite 是適用於 AMD 成本最佳化 FPGA 的單一精簡型開發工具。此工具可完全整合設計流程,包括從 RTL 設計到實作和除錯的所有必要功能。

無需苦惱時序收斂,享受開箱即用的成功體驗。使用 Vivado Design Suite,實現高效率設計並最大化生產力。

Vivado Design Suite 提供完全整合的解決方案,從模擬到除錯都包含在內,讓您不再需要昂貴的第三方工具,並能縮短上市時間。

Vivado Design Suite 提供強大、免費的 IP 目錄,內含 500 種以上的功能和 IP,適合各式各樣的應用。

AMD 提供領先的建構模塊,讓您快速輕鬆地保護、認證與整合系統元件。

透過 AMD 符合 CNSA 2.0 PQC 的安全啟動與多層級保護來保障您的系統:

透過包含下列項目的 TUV SUD 認證 AMD 安全設計流程,加快打入矽晶與軟體市場:

AMD 自適應 SoC 將多種功能整合到單一晶片中,達成提升效能、減少延遲和增強安全性的效果。

AMD 針對成本敏感的應用提供各式各樣的自行調適解決方案。AMD UltraScale+ 與 7 系列 FPGA 和自適應 SoC 以 LUT6 架構為基礎,不僅最大化效能,同時還能維持成本最佳化,適合對價格極為敏感的客戶。

開始使用 AMD 成本最佳化產品組合。

提供用於基準測試的完整設計套件。親眼見證。

本文提供的資訊僅供參考,可能會有所變更,恕不另行通知。沒有技術或產品是絕對安全的。GD-122。